1974年,惠普开发了微处理器来控制其产品中的各种功能,从软盘驱动器到电压表。这种简单的处理器不符合标准微处理器的要求-它甚至不支持加法或减法-因此被称为“纳米处理器”。纳米处理器的主要特点是低成本和高工作速度:与现代摩托罗拉6800的成本为360美元,纳米处理器的成本为15美元相比,控制操作要快得多。

尽管它没有加法运算,但是Nanoprocessor可以(缓慢地)通过重复递增或递减(它支持的运算)来加数。在其他情况下,例如,使用Hewlett-Packard的电压表将ALU芯片(74LS181)添加到产品中,然后进行快速添加-将它们作为I / O设备进行访问。自然地,完成图灵处理后,从理论上讲,纳米处理器可以完成从计算浮点函数到启动《孤岛危机》游戏的所有工作。那就太慢了。

可以从链接下载处理器照片模板(122 MB PSD)。

HP Nanoprocessor, 1820-1691. , -2,5 , – . , .

在随后的几十年中,该处理器一直不为人所知,直到最近它的开发商Larry Bauer与The CPU Shack共享了该芯片的光罩和文档。他们在那里扫描了光掩模,并写了一篇有关纳米处理器的文章。在Antoine Berkovichi将图像拼接成一个图像之后,我根据该图像对Nanoprocessor进行了评论。这是本文的第二部分,在讨论基于光掩模的反向工程时,我将讨论纳米处理器电路的一些细节。纳米处理器的功能块很有趣,因为它绕过了必需功能的最小实现,同时仍然是有用的微处理器。

内部纳米处理器

像那个时代的大多数处理器一样,纳米处理器是8位的。但是,它不支持随机存取存储器,并且代码是从外部2KB ROM执行的。它具有16个8位寄存器-比大多数处理器更多,并且足以弥补许多应用程序的内存不足。纳米处理器具有48条指令-大大少于Motorola 6800的72条指令。但是,纳米处理器具有一组方便的位设置,清除和检查操作的能力,这是当时其他处理器所没有的。它还具有几个支持I / O端口和通用I / O引脚的I / O命令,从而可以轻松地控制其他设备。

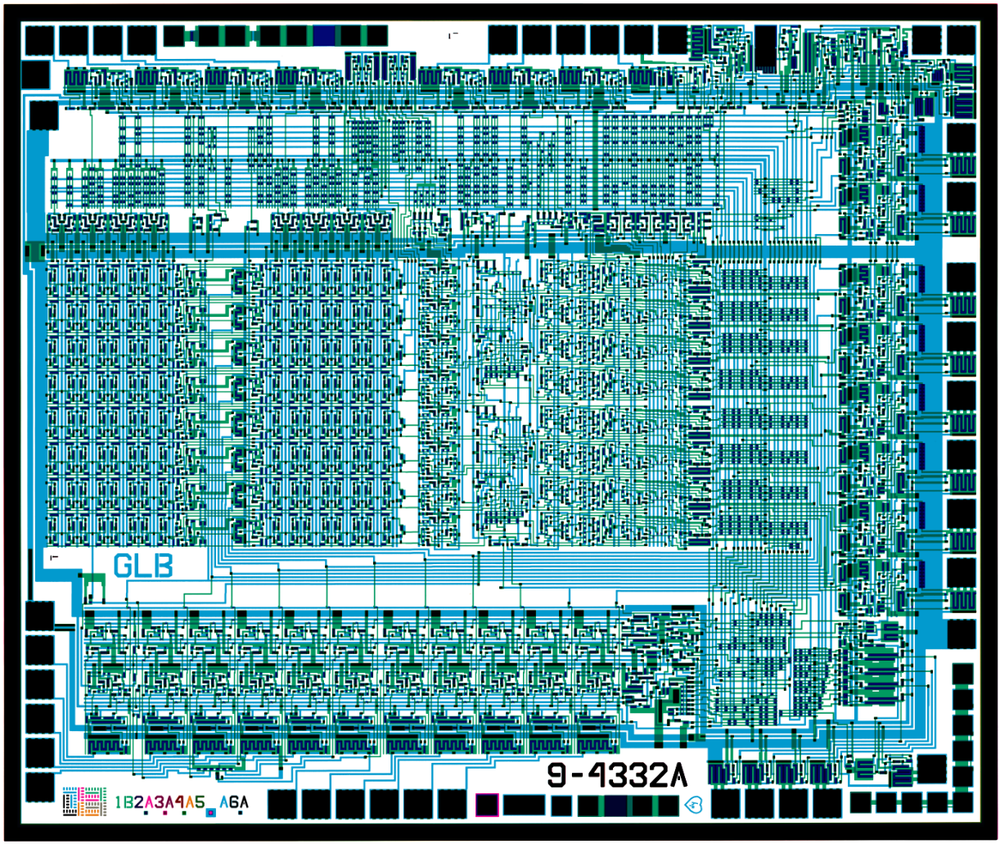

纳米处理器没有用于支持内存处理的指令,因为它是为不需要数据存储的操作而设计的。但是,在某些应用中,纳米处理器使用RAM作为I / O设备。地址被发送到一个I / O端口,并且从另一个I / O端口读取了一个字节的数据。组合的纳米处理器光掩模(可单击) 从上面的光掩模图像中,我们可以得出结论,纳米处理器很简单。蓝线是芯片顶部的金属导体,绿线是带有杂质的硅。外围有黑色正方形-40个焊盘,用于与IC的外部触点通信。里面的黑色小区域是晶体管。如果仔细观察,您可以算出其中的4,639个。

如果考虑到指令解码器是由成对的小晶体管组成的,这是为了方便组件的布置,并且将这些对计为一对,那么我们得到3829个晶体管。其中,1061为上拉电阻,2668为有源。相比之下,6502具有4,237个晶体管,其中3,218个处于活动状态。 8008具有3500个晶体管,而Motorola 6800具有4100。

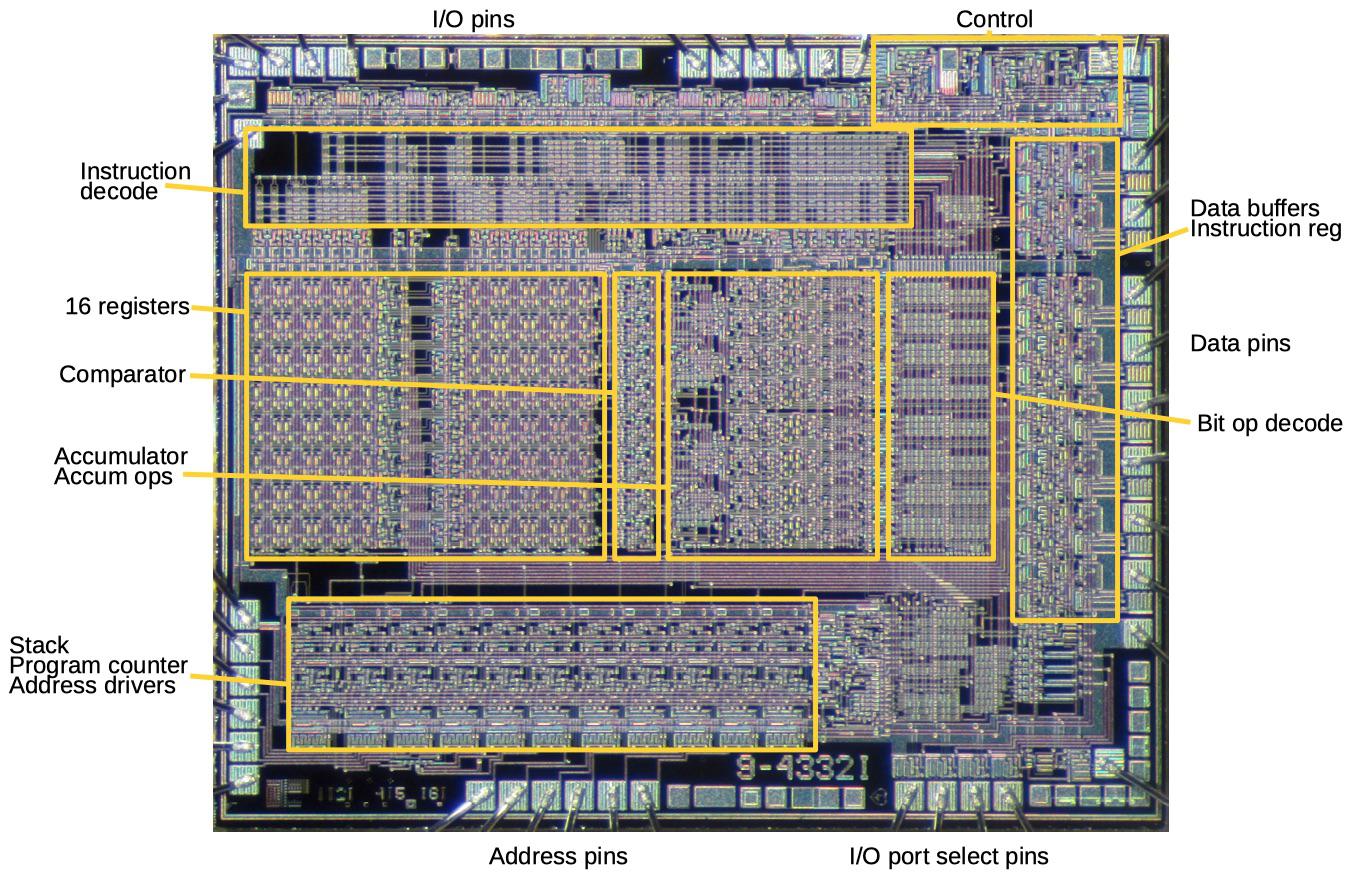

下面的框图显示了纳米处理器的内部结构。在中间有16个保持寄存器。比较器允许您比较两个值以提供条件分支。控制逻辑单元处理累加器的递增,递减,移位和位运算。它没有标准ALU的算术和逻辑运算。程序计数器(右)从指令寄存器(左)检索指令;中断和子例程调用具有其自己的单项堆栈,用于存储返回地址。

纳米处理器说明中的工作流程图

让我强调一下,尽管纳米处理器简单且缺乏算术运算,但它并不是切换控制线的某种“玩具”处理器。它是用于执行复杂操作的快速而强大的处理器。例如,HP 98035实时时钟模块使用Nanoprocessor处理两个打不同的ASCII控制字符串,并计算一个月中的天数。

一个有趣的有趣项目可以是创建FPGA版本的Nanoprocessor-因为Nanoprocessor可能是实际商用处理器的最简单版本。它的说明描述了所有命令,并提供了可以运行的代码示例。

寄存器

下面的晶体照片显示,纳米处理器的很大一部分被其16个寄存器占用。它们通过数据总线与其余组件通信。顶部的链条选择一个特定的寄存器。右侧比较器旁边的寄存器R0。

纳米处理器的重要部分由其16个寄存器占据

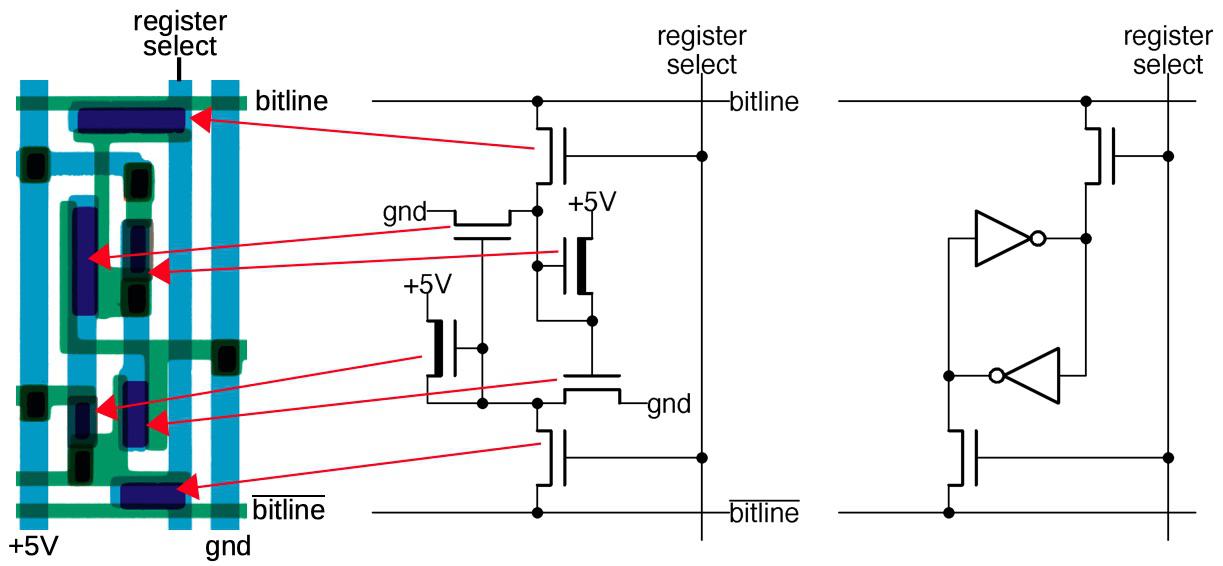

,一个寄存器的组成部分是反馈回路中的两个反相器,如下所示存储一位。如果顶部导体为0,则右侧逆变器将向底部导体输出1,然后左侧逆变器将向顶部导体输出0,从而完成循环。通过“记住” 0,电路保持稳定。以同样的方式,如果顶部导体为1,则其底部的极性反转为0,顶部的极性反转为1。网络可以以此方式存储0或1,从而形成1位存储位置。

稳定位存储电路中

的两个反相器下图显示了如何在芯片上实现这两个反相器存储。组件的物理位置基于光掩模显示在左侧。优化了布局,以使单元占用尽可能少的空间。蓝线-金属层,绿线-硅。中间是带有晶体管的相应电路图。每个逆变器均由一对晶体管组成,如右图所示。顶部和底部的晶体管-“直通”,它们提供对存储单元的访问。

在纳米处理器中存储一位。每个位在6个晶体管(6T SRAM单元)上实现。

寄存器集由这些位单元的矩阵组成。寄存器选择总线选择一个寄存器(一列)进行读取或写入。然后,上下传输晶体管将反相器连接到它们各自的水平位线。为了读取,高位线提供了存储在单元中的值;寄存器中存储的八位有八位线。为了进行写入,该值被传送到高位线,而反转的值被传送到低位线。这些值取代了反相器的信号,使它们取所需的值并存储该位。因此,水平位线和垂直选择线的网格允许将值读取或写入特定寄存器。

解码命令

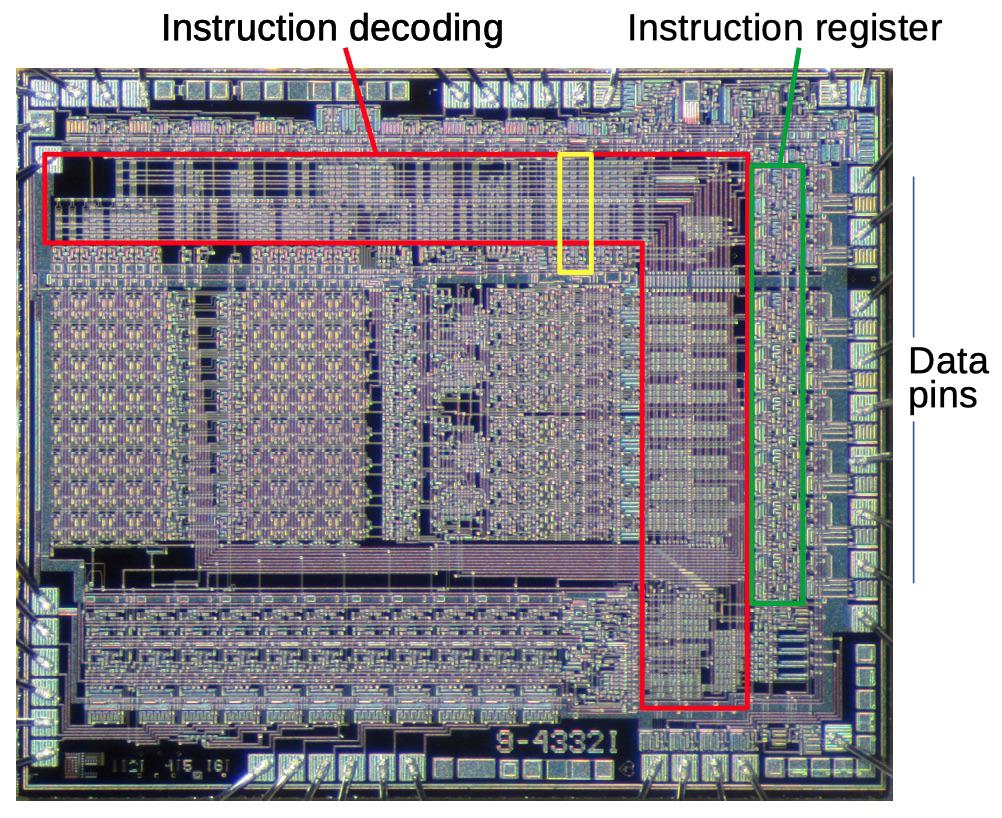

解码电路负责获取指令的二进制代码(例如01101010),并确定指令是什么(在这种情况下,为“来自寄存器10的负载累加器”)。与许多处理器相比,Nanoprocessor的指令非常简单:它的数量相对较少(48),并且指令代码始终为一个字节。下图显示了指令解码逻辑(红色)占据了芯片的很大一部分。指令寄存器(绿色)是一组八个锁存器,用于保存当前指令。命令寄存器位于命令来自ROM的数据引脚旁边。在本节中,我们将分解显示为黄色的解码链。

解码由“或非”门完成。每个或非门可识别特定命令或命令组。或非门接受命令位或其补码作为输入。当所有输入位均为零时,“或非”门报告匹配。这样,您既可以在整个团队中,也可以在团队的一部分中搜索比赛。例如,命令“来自寄存器R的负载累加器”具有二进制格式0110rrrr,其中后四位指示所需的寄存器。或非门(bit7 + bit6'+ bit5'+ bit4)'将与此命令匹配。

以这种方式构造的指令解码器是好的,因为它可以由紧凑且重复的电路组装而成。它通常称为PLM(可编程逻辑阵列)。这个想法是矩阵的输入信号是水平馈送的,输出信号是垂直馈送的。在每个交叉点处可以有一个晶体管,然后输入信号是门的一部分。如果没有晶体管,则忽略此输入。结果是紧凑地布置了NOR阀。在早期的微处理器中,解码器通常由NOR门矩阵构成-例如,6502就是这种情况。

下图在右侧显示了三个放大的解码器,在上图中以黄色圈出。该图对应于最左边的解码器。注意图中的晶体管与布局上晶体管的粉红色斑点的对应关系。这个想法是,如果任何输入信号激活了晶体管,那么晶体管会将输出拉至地。否则,输出将通过电阻上拉。底部的逆变器放大信号,以便有足够的电流为电池的所有八个部分供电。有趣的是,这种布局使用了接地和输出相连的成对晶体管-我认为仅使用一个晶体管没有任何优势。无论如何,请注意PLM如何提供密集的解码器排列。

请注意,指令解码器中的反相器被上拉至12 V,而不是5V。这是因为纳米处理器使用金属栅极晶体管,而不是该时代其他微处理器中使用的更高级的硅栅极晶体管。具有金属栅极的晶体管的缺点是阈值电压增加,因此晶体管的输出电压远低于栅极的电压。传统反相器的输出太小,无法馈入直通晶体管的栅极,因为其输出电压将再次下降。解决方案是为解码器的逆变器使用12 V电源来控制电池旁路晶体管,然后信号将具有足够的电压来激活直通晶体管。换句话说,纳米处理器需要额外的12+ V,因为它使用金属栅晶体管而不是更高级的硅栅晶体管。

纳米处理器解码器电路之一。左侧的图对应于右侧所示的三个解码器中最左侧的解码器。

该电路产生递增/递减信号,该信号被馈入累加器电路。当时钟,请求,第6个命令位和第2个命令位的信号电平低时,梯级检测到匹配-在执行阶段发现匹配为x0xxx0xx。这些命令包括“增量二进制”(00000000),“增量BCD”(00000010),“减量二进制”(00000001)和“减量BCD”(00000011)。

图中所示的链使用x0xxx0xx形式的命令查找匹配项,因此找到的匹配项不只是递增和递减命令。为什么不寻找完整的比赛?原因是如果不使用累加器,则增量/减量信号的激活无关紧要。通过扩展匹配选项列表,开发人员可以摆脱电路中的某些晶体管。重要的是,链条应覆盖其他与电池相关的指令,例如“清除累加器”(00000100)或“来自寄存器的负载累加器”(0110rrrr)。

比较器

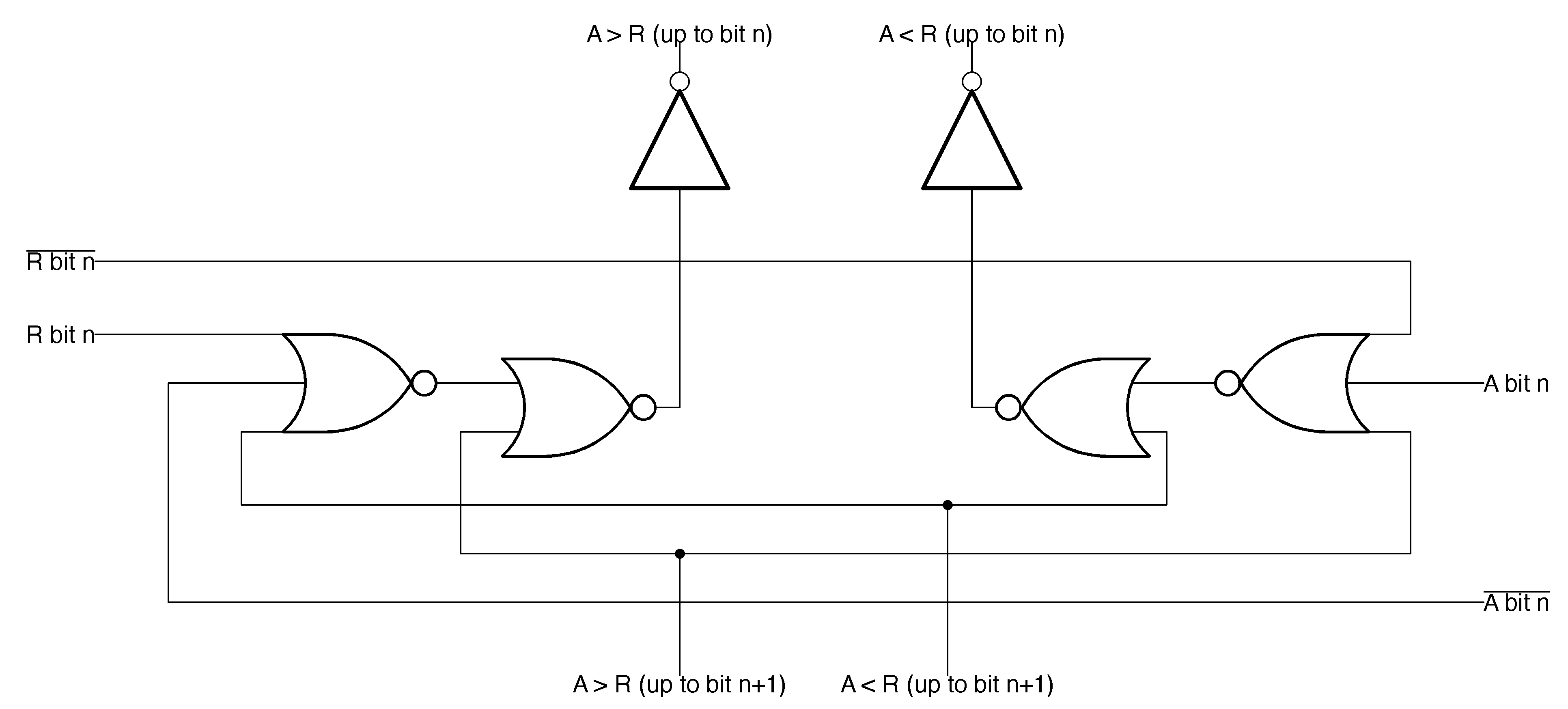

重要的纳米处理器电路是一个比较器,用于将累加器中存储的值与R0寄存器中的值进行比较。比较器使用单个但棘手的电路进行比较。本质上,该算法会比较两个数字(从最高有效位开始)。如果位相等,则继续到较低的位。第一个位差确定哪个值更大(例如,在10101010和10100111的情况下,这确定从右起的第4个位)。

该算法分八步实施,一次一步,从底部的最高有效位开始。每个步骤都由两个对称部分组成-一个确定不等式A> R0是否成立,而其另一部分检查不等式A <R0。如果数量仍然相等,但在此阶段发现差异,则该阶段会产生“更多”或“更少”的信号。否则,它将决策下移。最终决定由最顶层的梯级决定。请注意,比较器中相等性的比较是``免费''进行的-如果输出中没有信号``更多''或``更少'',则值相等。

8位比较器的阶段之一

下图显示了比较器两个阶段的物理布局。比较器布局中的一个技巧是,它位于左侧的寄存器0和右侧的累加器之间,从而最大程度地减少了导线的长度。比较器直接访问寄存器0,而绕过通常的寄存器和数据总线选择路径。

比较器分为两级-在光罩上指定

纳米处理器的条件分支命令可以检查比较器输出。条件分支电路非常简单:分支指令的几位通过多路复用器选择特定的检查。然后,该命令的第7位决定是选择“如果为true时是此分支”还是“如果为false则是此分支”。与大多数处理器不同,纳米处理器不允许分支到任何地址。如果满足条件,它将仅跳过两个命令字节(通常这两个字节包含转到所需目标的命令,但有时还有其他命令)。跳过方案很简单:再次调用程序计数器,同时不将值增加1,而是增加2,从而跳过两个命令。事实证明,纳米处理器在相对较少的网络上实现了广泛的条件检查。

纳米处理器具有大量的分支条件-对于这样一个简单的处理器而言,出奇的大。您可以检查以下条件:A> R0,A> = R0,A <R0,A <= R0,A == R0,或A!= R0。此外,条件分支可能取决于累加器中的值是否为零,累加器中存储的值的特定位是否等于零,是否设置了溢出标志或是否设置了I / O寄存器。

电池和控制逻辑设备

累加器是一个特殊的8位寄存器,用于存储当前正在处理的字节。电池的操作由控制逻辑设备(ULU)进行,该逻辑在处理器的说明中称为“纳米处理器的心脏”。 ULU与大多数处理器中的算术逻辑单元(ALU)等效,只是它不执行算术或逻辑运算。同时,ULU并不像乍看起来那样毫无用处。它可以以二进制或二进制十进制代码(BCD)递增或递减累加器中的值。 BCD在一个字节中存储两位小数。这对于I / O或显示非常有用。同样,ULU可以找到累加器的二进制补码或对其进行重置,以及设置并清除某个位。最后,它支持左右移位操作。

电池相关电路上

图显示了电池和ULD电路。在第一部分中,放置了各种网络,定义了一个零值,支持BCD,并提供了进位滑动-从最低有效4位快速生成进位。第二部分包含主电池和ULU电路。第三部分将控制信号从上面的解码逻辑分发到累加器的八个部分。最后一部分包含指令解码逻辑,该逻辑解码位运算并将信号发送到累加器的所需部分。

累加器/ ULU的主体由8个部分组成,每个部分一位,最低有效位在顶部。我们将从每个部分看一下四个电路:一个用于增/减操作的进位发生器,一个用于增/减操作的位发生器,一个用于选择新累加器值的多路复用器以及一个用于存储累加器值的锁存器。

增量/减量设备的每个部分(以下)使用半加法器实现。增量/减量链的方向决定了操作码:操作码低位的0表示增量,而递减的1。左侧的进位链产生一个进位信号。要递增,请在接收到进位输入并且当前位为1时创建一个进位输出(因为它将被递增为二进制10)。对于减量,进位线发出借位信号,因此当存在进位输入(即借位)且当前位为0时,会生成进位输出

。增量/减量链的一部分

右侧的梯级以递增或递减的方式更新当前位。存在进位输入时,将切换当前位-本质上是通过三个NOR门的XOR实现。困难之一是调整BCD。对于BCD递增操作,当数字9递增时进位发生;对于BCD递减操作,数字0递减至9,而不是二进制1111。

多路复用器管理各种电池操作。根据操作,一个通过晶体管被激活,选择所需的值。例如,对于递增/递减操作,上部晶体管从上述递增/递减电路中选择输出。晶体管激活先前描述的指令解码器,该指令解码器已找到相应的增量/减量指令。同样,右移命令通过向每个累加器部分施加n +1个电池位以使该值移位,从而激活右移晶体管。

用于存储电池一位的锁存器和选择电池输入的多路复用器的电路

锁存器为累加器存储一位。当电池保持晶体管被激活时,两个或非门形成一个保持环路。如果改为激活电池负载晶体管,则电池会从多路复用器加载所需的值。清除n位并设置n位的行允许命令更改累加器的各个位;然后,多路复用器立即更新累加器的所有位。

计数器和程序寻址

另一个较大的链块是位于纳米处理器左下角的11位程序计数器。同样在此块中,有一个锁存器存储子程序的返回地址,另一个锁存器在中断后存储程序计数器。将它们视为一个元素长的堆栈。软件计数器具有一个递增设备,负责移至下一个命令。它还知道如何一次增加两个,从而允许条件分支指令跳过两个指令(这种增加设备仅通过增加第一个位而不是第0位来实现)。为了加快增量装置的操作,它具有结转功能;如果所有六个最低有效位均为1,它将立即递增第6位,而无需等待进位通过所有最低有效位。

控制和时钟频率

纳米处理器的最后一部分是控制电路。与其他微处理器相比,纳米处理器控制方案似乎微不足道:处理器从请求时钟转到执行时钟再返回(带有周期性中断)。控制电路只是几个触发器和门,因此无需多说。

结论

下图显示了纳米处理器的主要功能块。纳米处理器非常紧密地适合它们,这比我过时的金属快门技术所期望的要好得多。逆向工程表明,这些功能块是通过简单但经过精心设计的电路实现的。

纳米处理器使用金属栅晶体管,而其他微处理器已经开始使用硅栅晶体管已有几年了。这种差异看似难以理解,但对组件的位置有重大影响:在制造带有硅栅极的晶体管时,会增加一层带有导体的多晶硅。由于您可以随意使用两层可以穿过相邻层的导体,因此可以更轻松地放置组件。如果只有金属层,则放置部件会更加困难,因为导体会挡住它们。在其他我研究过的芯片中,使用了金属栅晶体管技术,组件的布局令人作呕-一堆缠结的导线将信号带到每个晶体管,这使晶体管的密度较低。另一方面,纳米处理器功能块经过精心设计,所有信号都可以很好地相处。例如,数据总线有一些额外的空间,但是总的来说,我对纳米处理器布局的密度印象深刻。

基于我逆向工程

纳米处理器的纳米处理器功能组件-处理器很不寻常。乍一看,由于缺乏基本的算术运算,在我看来它甚至是“伪处理器”。但是,在更详细地研究之后,我仍然印象深刻。其简单的设计使其可以比当时的其他处理器更快地运行。该命令集可以做的不只是眼球。惠普(Hewlett-Packard)在1970年代和1980年代的许多产品中都使用了Nanoprocessor,其作用比预期的要复杂得多,例如,解析字符串和执行计算。出版了他的面具之后,由于Nanoprocessor的工作,我们可以了解链条的所有秘密。

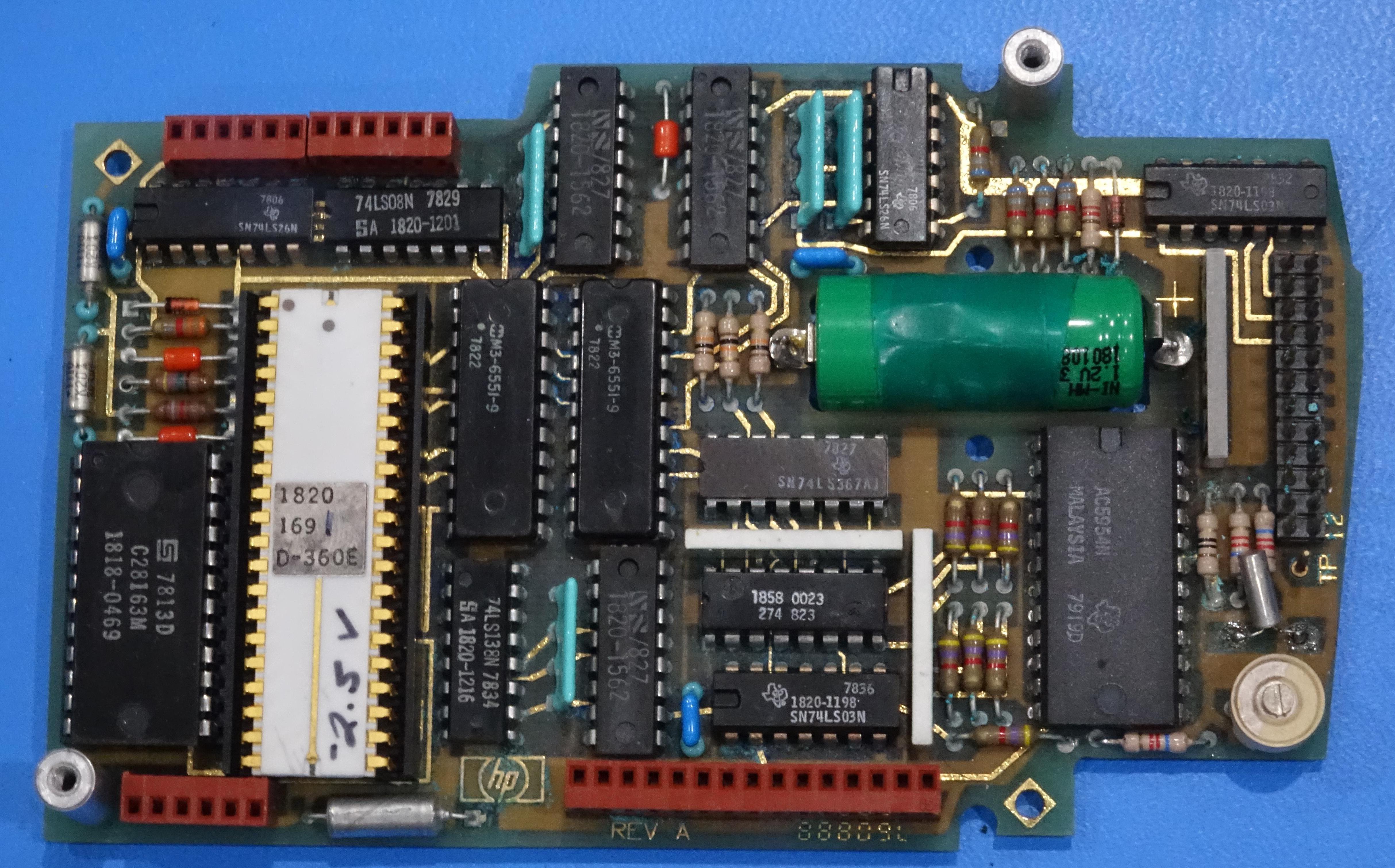

纳米级处理器(白芯片)是惠普精密计时模块的一部分。注意手写电压;每个芯片都需要自己的偏置电压。