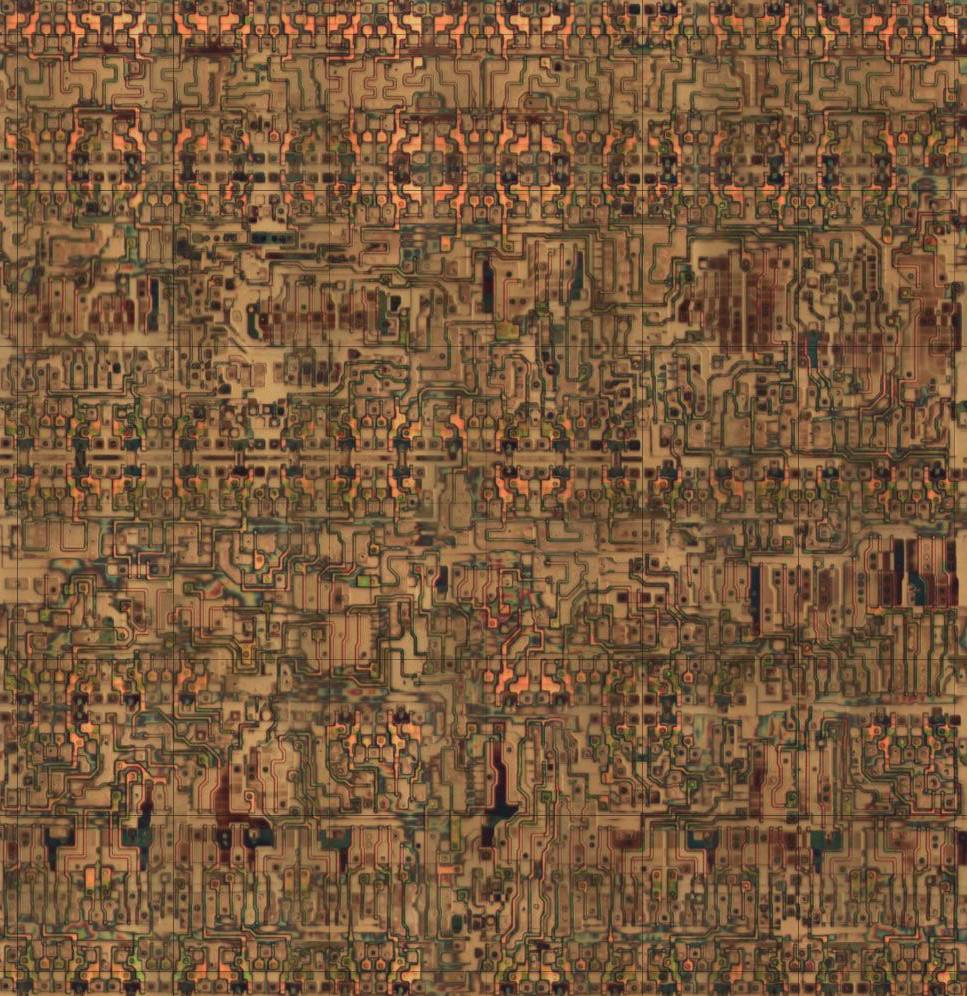

图为XC2064芯片的64个模块之一。去除了金属化层,我们可以看到位于金属化层下方的硅和多晶硅晶体管。您可以在此处看到更大的照片:siliconpr0n。

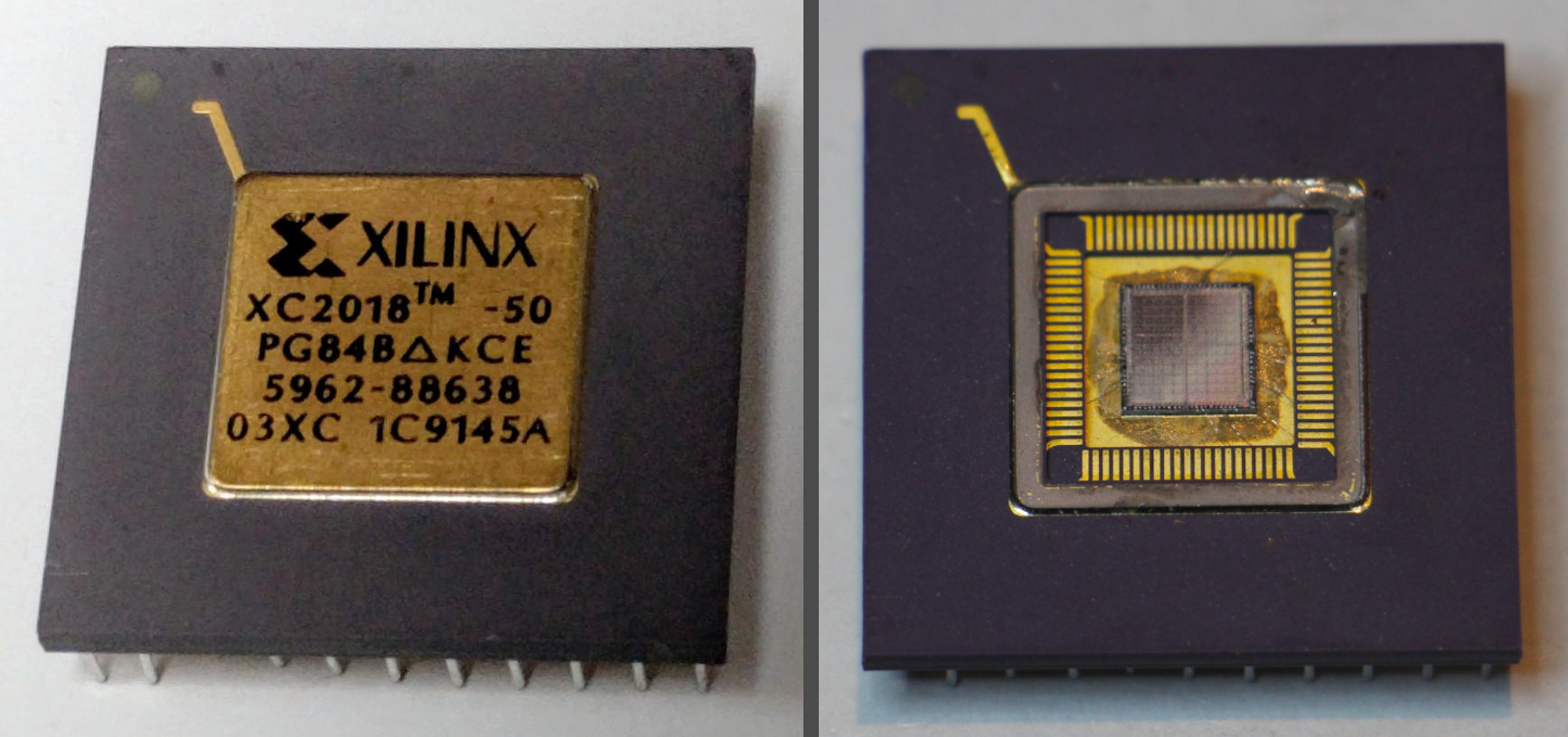

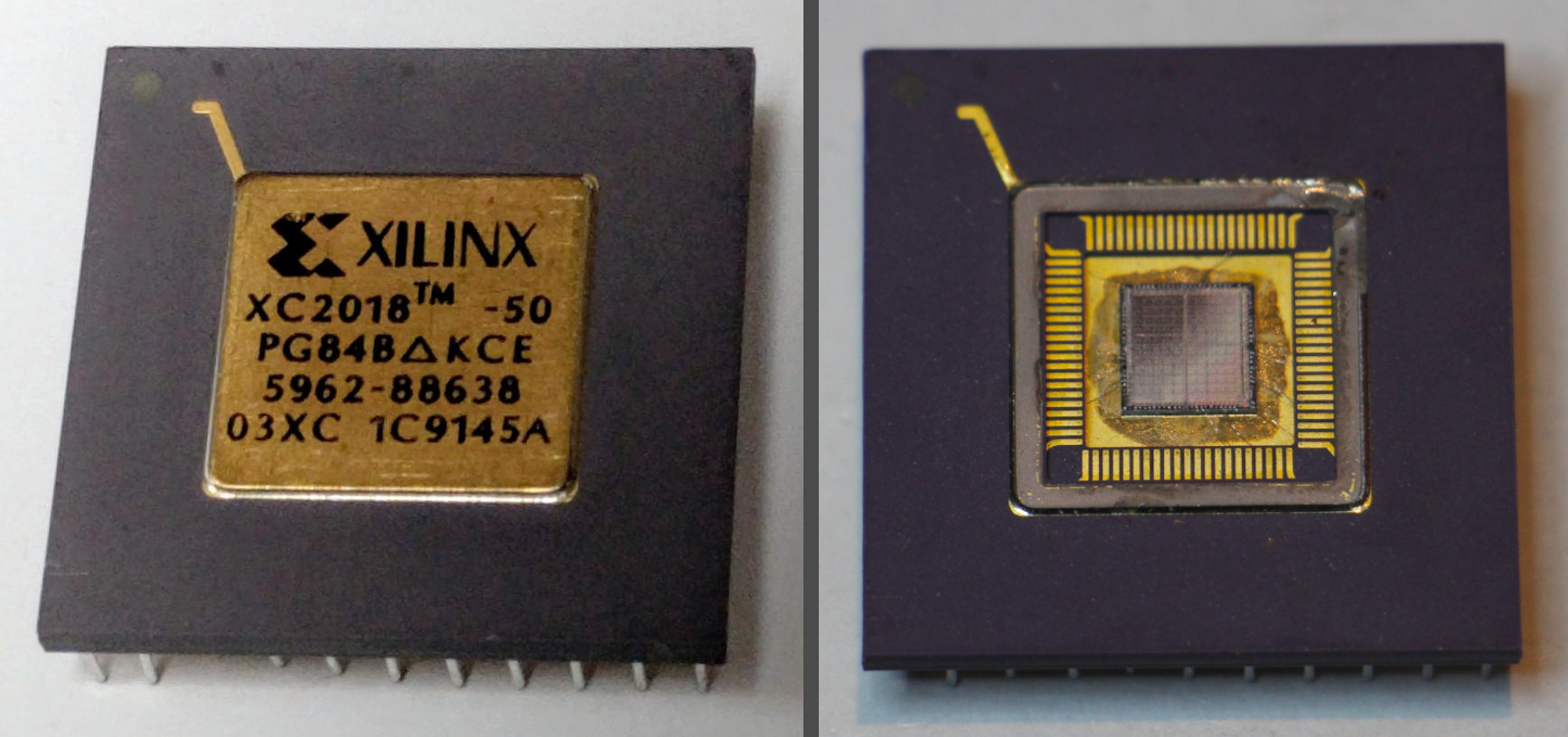

FPGA由Xilinx的共同创始人Ross Freeman于1984年发明,第一个FPGA是XC2064。与现代FPGA相比,它要简单得多,仅包含64个逻辑块,而现代FPGA则是成千上万种,它的产生催生了一个价值数十亿美元的产业。XC2064非常重要,以至于它进入了芯片名人堂。我对XC2064进行了反向工程,在这篇文章中,我以一般的术语解释了其内部结构以及如何使用比特流对其进行编程。

赛灵思

Xilinx -. , , Xilinx , . Xilinx Seiko Epson Semiconductor Division ( Seiko Epson).

XC2064

: ( ) . — (Programmable Logic Devices, PLD), , , 1967 . , , , . , PROM, , , EPROM, . , , Programmable Logic Array, Programmable Array Logic (1978), Generic Array Logic Uncommitted Logic Array. , , « », . , , , , , . , . "Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology." "A Brief History of FPGAs".

Xilinx XC2064是第一款FPGA芯片。从这里获取:Siliconpr0n。

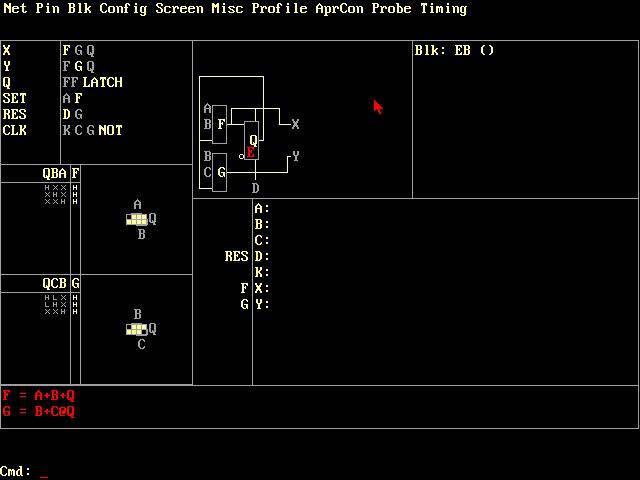

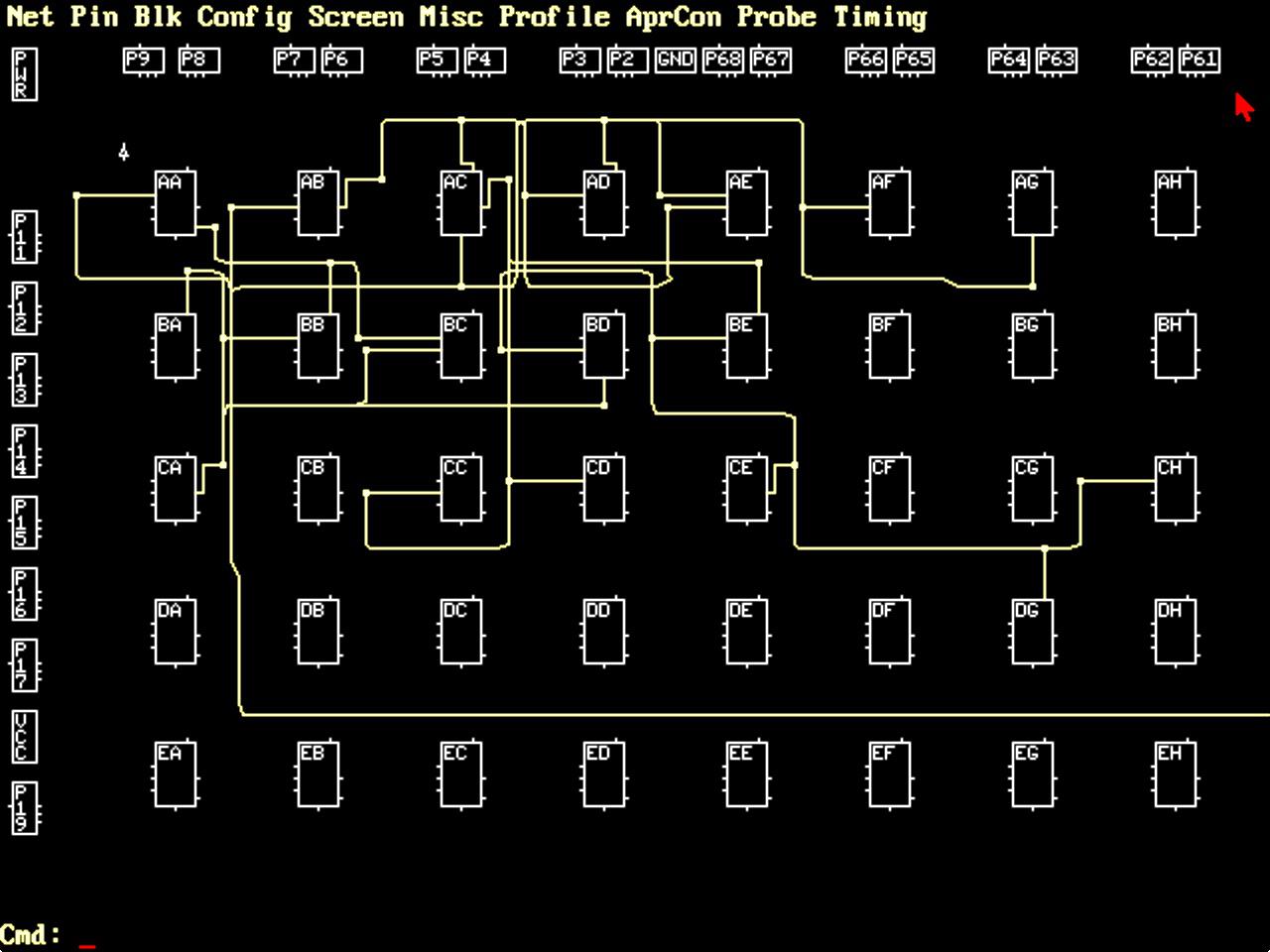

FPGA目前使用Verilog或VHDL等硬件描述语言进行编程,但当时Xilinx提供了自己的开发软件,即名为XACT的MS-DOS应用程序,价格高达12,000美元。 XACT的工作水平低于现代工具:如下面的屏幕快照所示,用户定义了每个逻辑块的功能以及逻辑块之间的连接。

XACT对连接进行路由,并生成一个配置文件(位流),该文件已加载到FPGA中。

XACT的屏幕截图。两个表F和G实现了屏幕底部所示的方程式,卡诺图显示在上方。

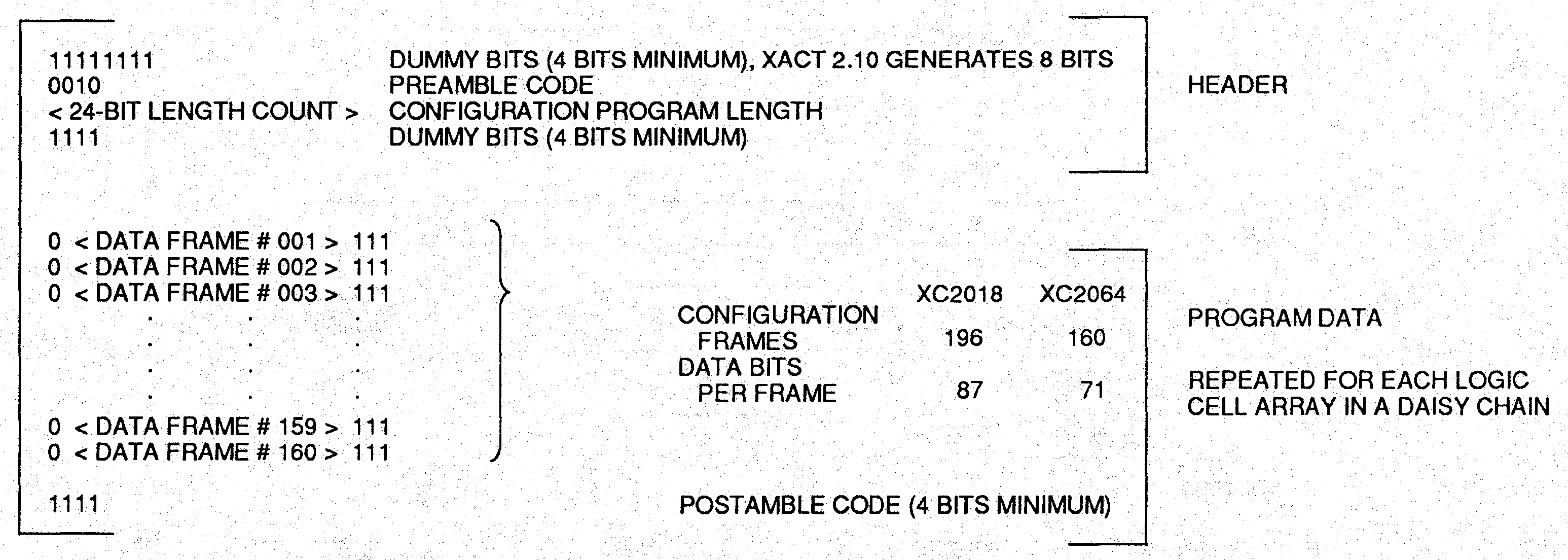

使用位流(专有格式的位序列)配置FPGA。如果您查看XC2064比特流(如下),您将看到神秘的图案混合,这些图案以不规则的方式重复出现并散布在整个比特流中。但是,研究FPGA的物理电路可以揭示比特流的数据结构,并且可以对其进行研究。

XACT生成的部分比特流。

FPGA如何工作?

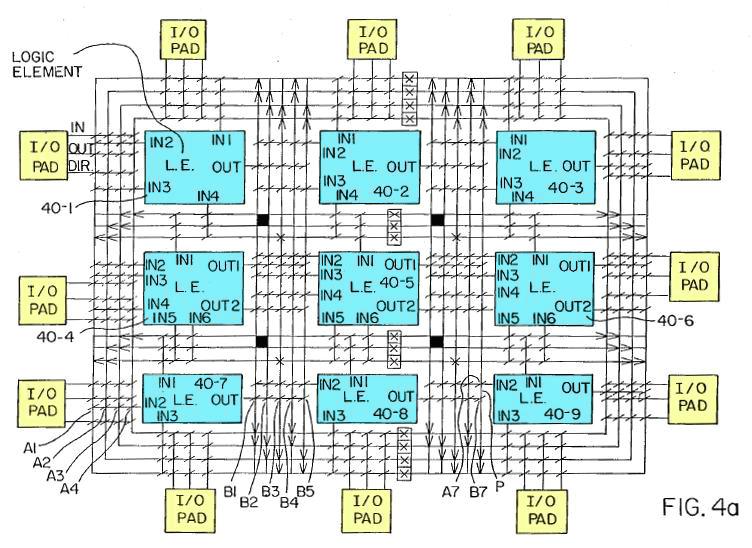

下图取自原始的FPGA专利,显示了FPGA的基本结构。这种简化的FPGA共有9个逻辑块(蓝色标记)和12个I / O端口。互连网络将组件连接在一起。通过在连接上设置开关(对角线),逻辑块可以相互连接,也可以与I / O端口连接。每个逻辑元件均可针对所需的逻辑功能进行编程。结果,这样的可编程芯片可以实现适合可用空间的任何设备。

FPGA专利,逻辑块(LE)互连。

可配置逻辑块(CLB)

尽管上图显示了9个CLB,但XC2064具有64个CLB。下图显示了CLB的结构。 CLB具有4个输入(A,B,C,D)和两个输出(X和Y)。介于两者之间的是组合逻辑,可以将其编程为任何所需的逻辑功能。 CLB还包含一个触发器,触发器的存在使您可以实现计数器,移位寄存器,状态机和其他有状态电路。梯形表示多路复用器,可对其进行编程以传递来自任何输入的信号。多路复用器允许您通过选择特定信号来控制触发器和输出,从而为特定任务配置CLB。

XC2064中的可配置逻辑块,取自此处:数据表。

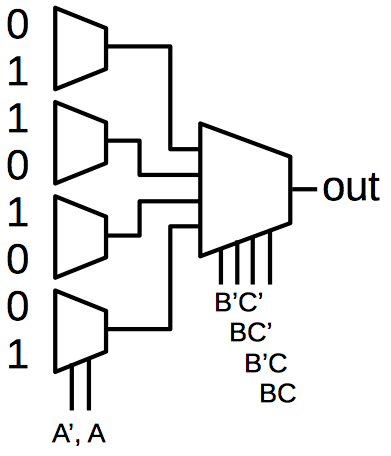

您可能想知道组合逻辑如何实现任意逻辑功能。在一组AND,OR,XOR等之间可以选择吗?不,有一个巧妙的技巧叫做查找表(LUT),它实际上是函数的真值表。例如,由8行的表定义了三个变量的函数。LUT包含8位存储器。我们可以在保留这三个位的同时实现任何3输入逻辑功能。

查看表格

XC2064 — , . CLB . XC2064 , 4 . , .

XC2064 . .

XC2064 . .

连接数

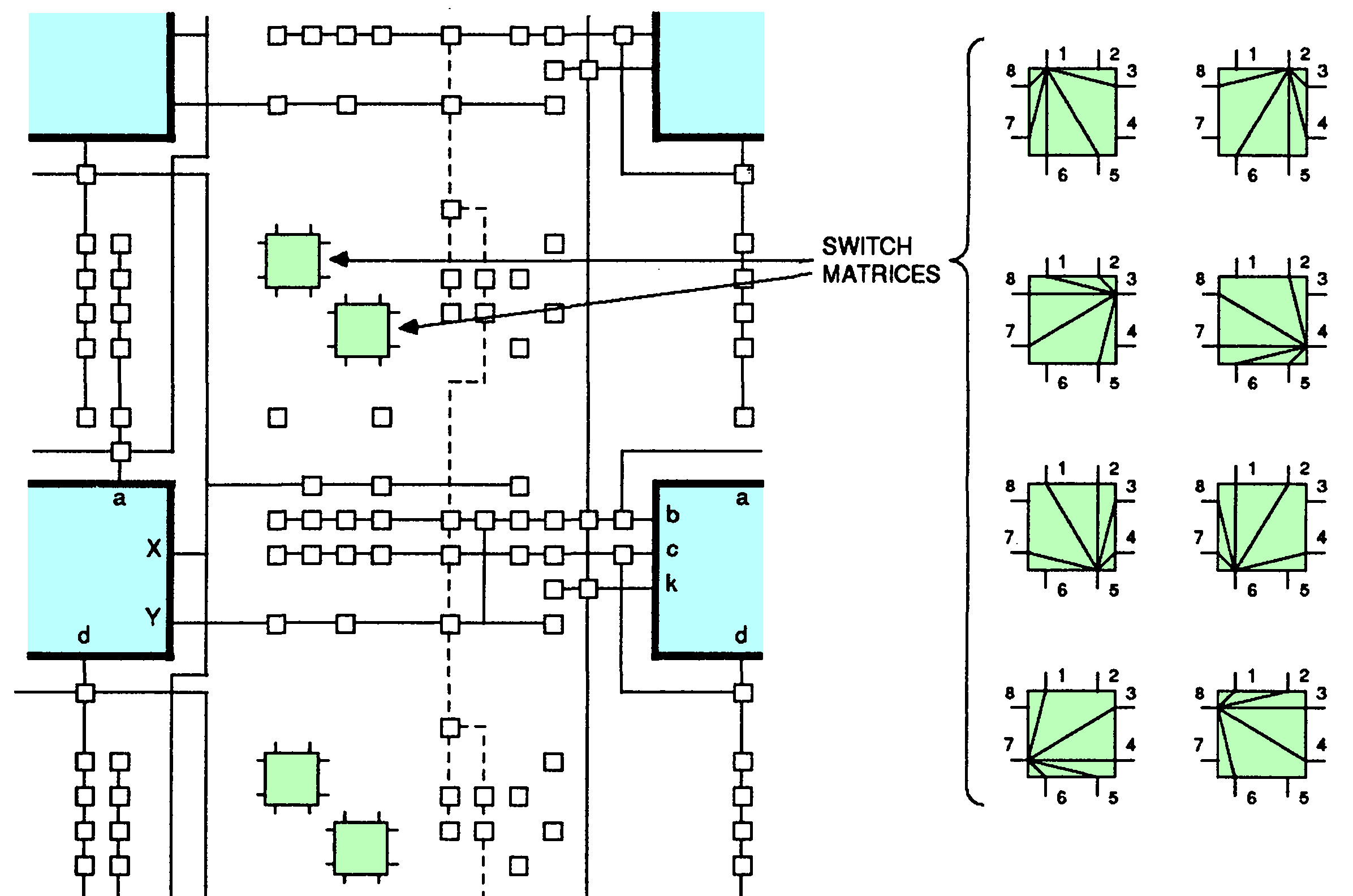

FPGA的下一个关键方面是连接,可以对它们进行编程以多种方式切换CLB。连接很复杂,但是粗略的描述是所有CLB之间都存在垂直和水平连接段。您可以将CLB连接到水平线和垂直线,并创建任意连接。连接的一种更复杂的类型是“开关矩阵”。每个矩阵有8个可以以任何方式相互连接(几乎)的引脚。

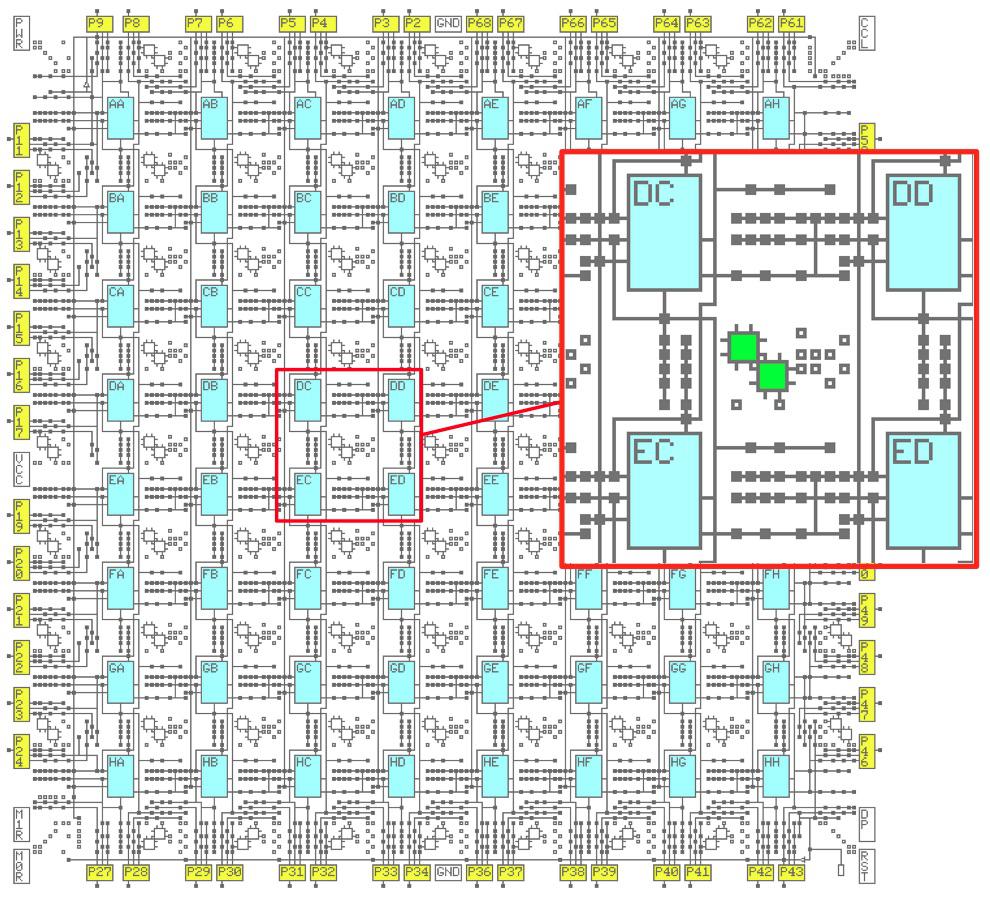

下图显示了XC2064链接的结构,这些链接提供了逻辑块(蓝色)和I / O线(黄色)之间的连接。插图显示了耦合机制的细节。绿色矩形是8针开关矩阵,小正方形是可编程的连接点。

XC2064 FPGA具有8x8 CLB矩阵。每个CLB都有一个从AA到HH的名称。

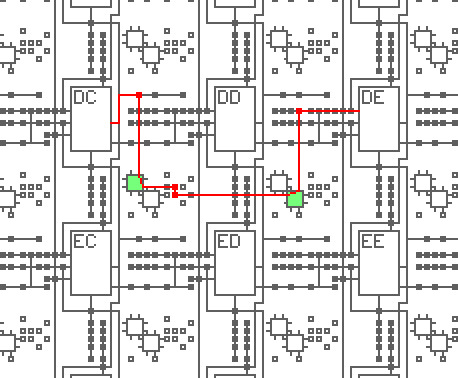

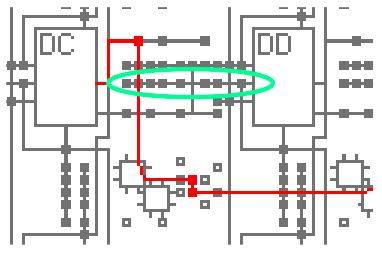

该连接可以将例如DC块的输出切换到DE块的输入,如下所示。红线显示信号路径,红色小方块显示已激活的连接点。从DC模块出来的信号被路由到8针开关(绿色)上的第一个连接点,该信号通过两个连接点和另一个8路开关(未使用的垂直和水平线未显示)路由。请注意,连接非常复杂,即使是这么短的路径也要使用四个连接点和两个开关。

从DC模块的输出到DE模块的示例信号路由。

下面的屏幕快照显示了如何在XACT中进行跟踪。黄线显示逻辑块之间的连接。随着信号数量的增加,很难在没有路径之间冲突的情况下进行连接。XACT自动跟踪,但是也可以手动编辑跟踪。

XACT程序的屏幕截图。它是一个MS-DOS程序,由键盘和鼠标控制。

实作

接下来,我们将通过晶体照片的反向工程研究XC2064的内部电路。请注意,这需要对XC2064有所了解。

水晶照

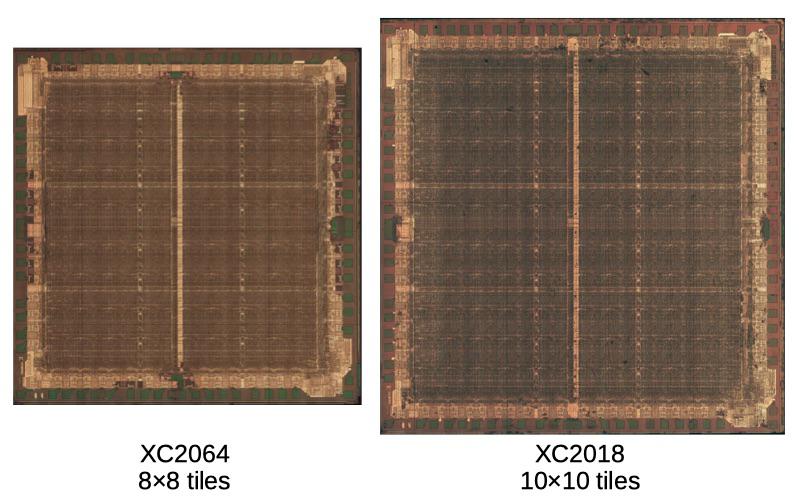

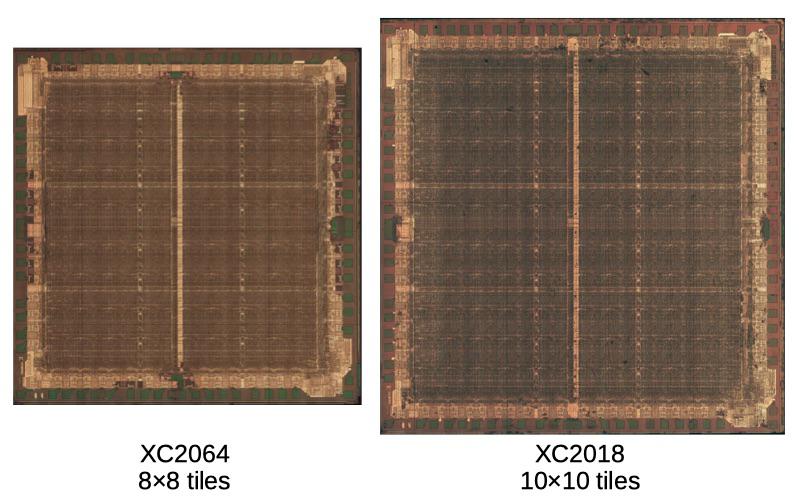

XC2064 XC20186, XC2064 XC2018 siliconpr0n. , . John McMaster , , . , .

XC2064 , John McMaster.

XC2064 , John McMaster.

XC2018

Xilinx XC2018 ( ) 100 , , XC2064. , XC2064 64 , 1010, 88. XC2018 , .

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

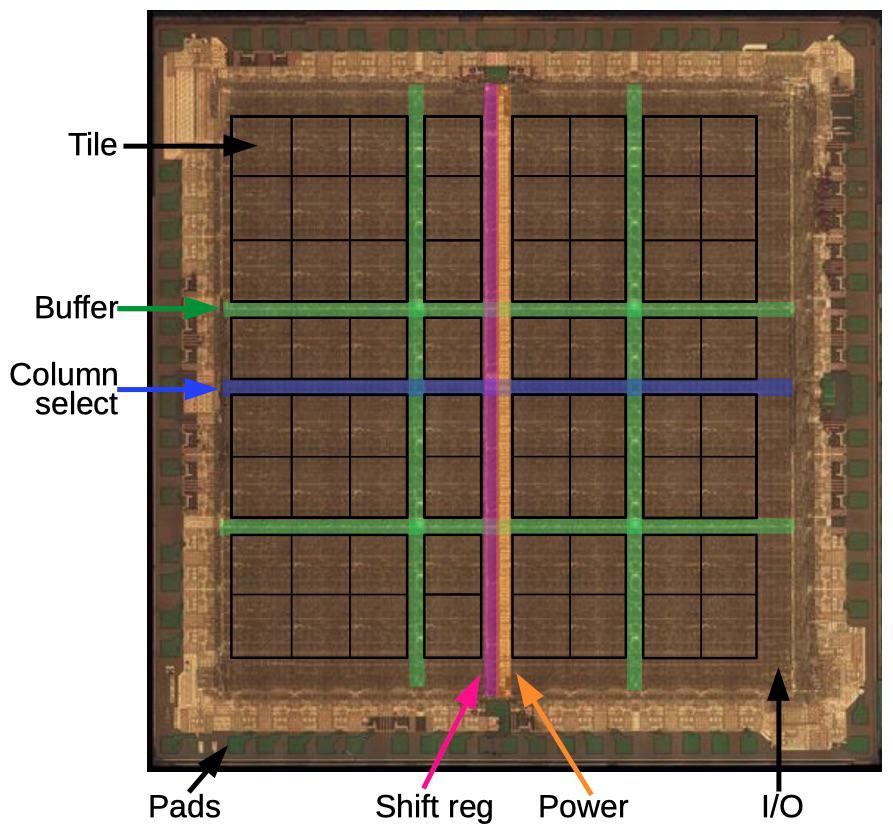

下面是XC2064晶体的照片。 FPGA的主要部分是一个8x8块的矩阵,每个块包含一个逻辑块和周围的电路。尽管FPGA图将逻辑块(CLB)与实体接线图分开显示,但实际上并非如此。实际上,每个逻辑块及其环境都实现为单个节点(图块)。 (确切地说,图块在每个CLB的顶部和左侧均包含连接。)

XC2064块布局。从这里获取:Siliconpr0n。

I / O模块位于集成电路的两侧,提供与外界的通信。它们连接到晶体的引脚(如绿色小方块所示),并连接到微电路盒的引脚。模具上有缓冲区(绿色):两个垂直和两个水平。这些缓冲器可放大在芯片上传播很长距离的信号,并减少延迟。垂直移位寄存器(粉红色)和水平列获取链用于将位流加载到芯片中,如下所示。

瓷砖内

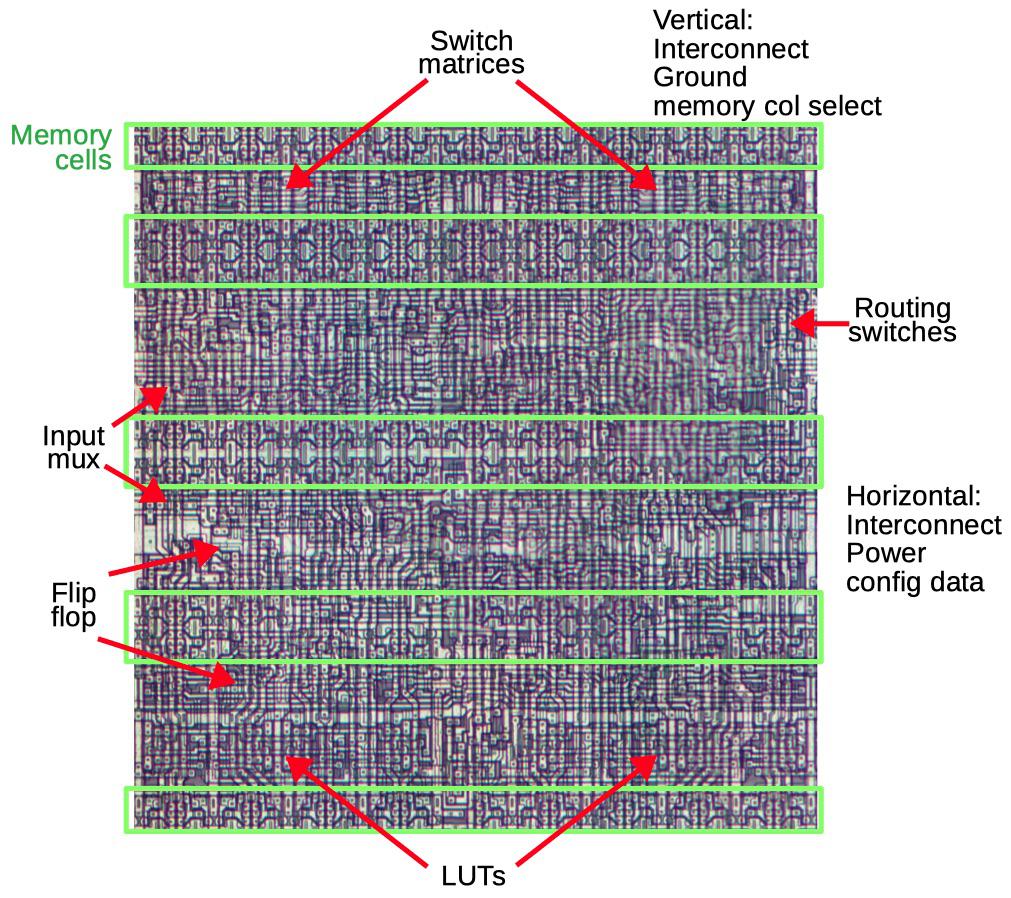

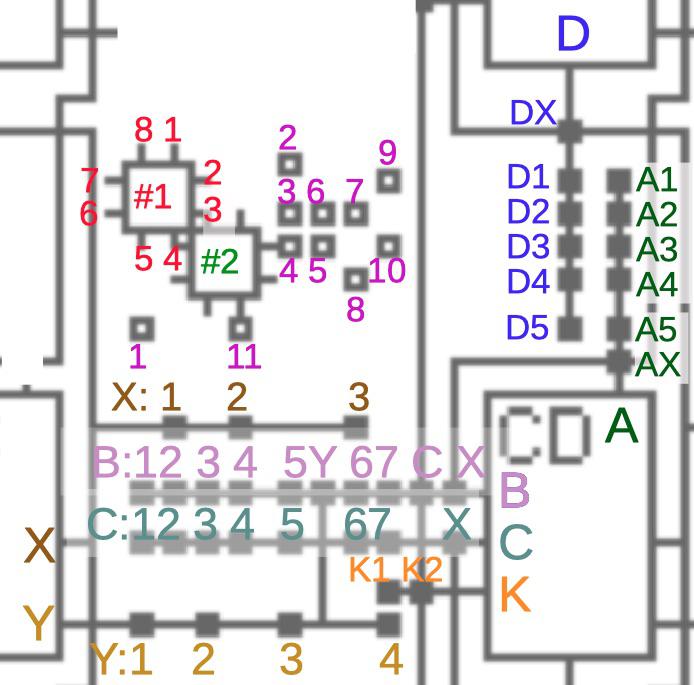

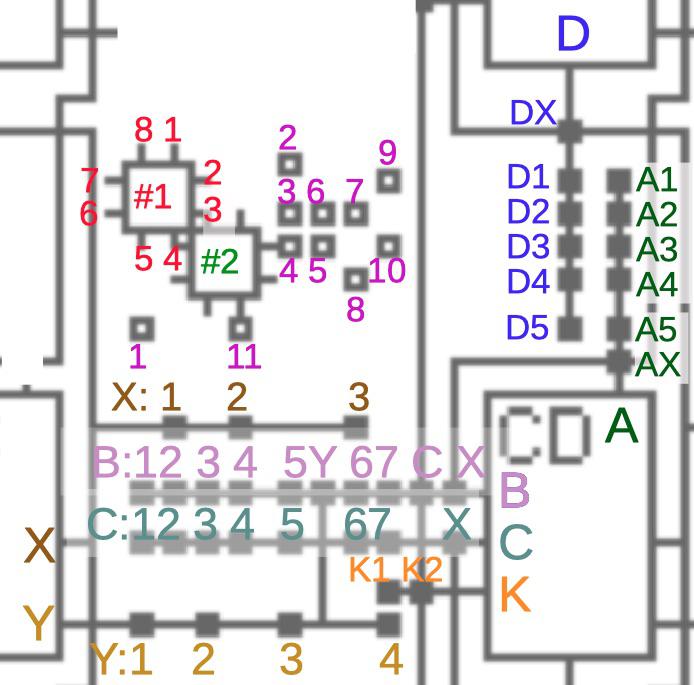

下图显示了一个XC2064磁贴的结构,该芯片包含64个封装在一个芯片上的磁贴。每个图块约有40%被存储配置位的存储单元(以绿色显示)占用。磁贴的顶部三分之一(大约)包含连接图:两个开关矩阵和多个单独的链路开关。以下是逻辑块。逻辑块的主要部分是输入多路复用器,触发器和查找表。磁贴通过水平和垂直通信线连接到邻居,并且还连接到电源和接地轨。配置数据位水平进入存储单元,垂直信号选择要加载的特定列。

一个FPGA磁贴显示重要的功能节点

晶体管

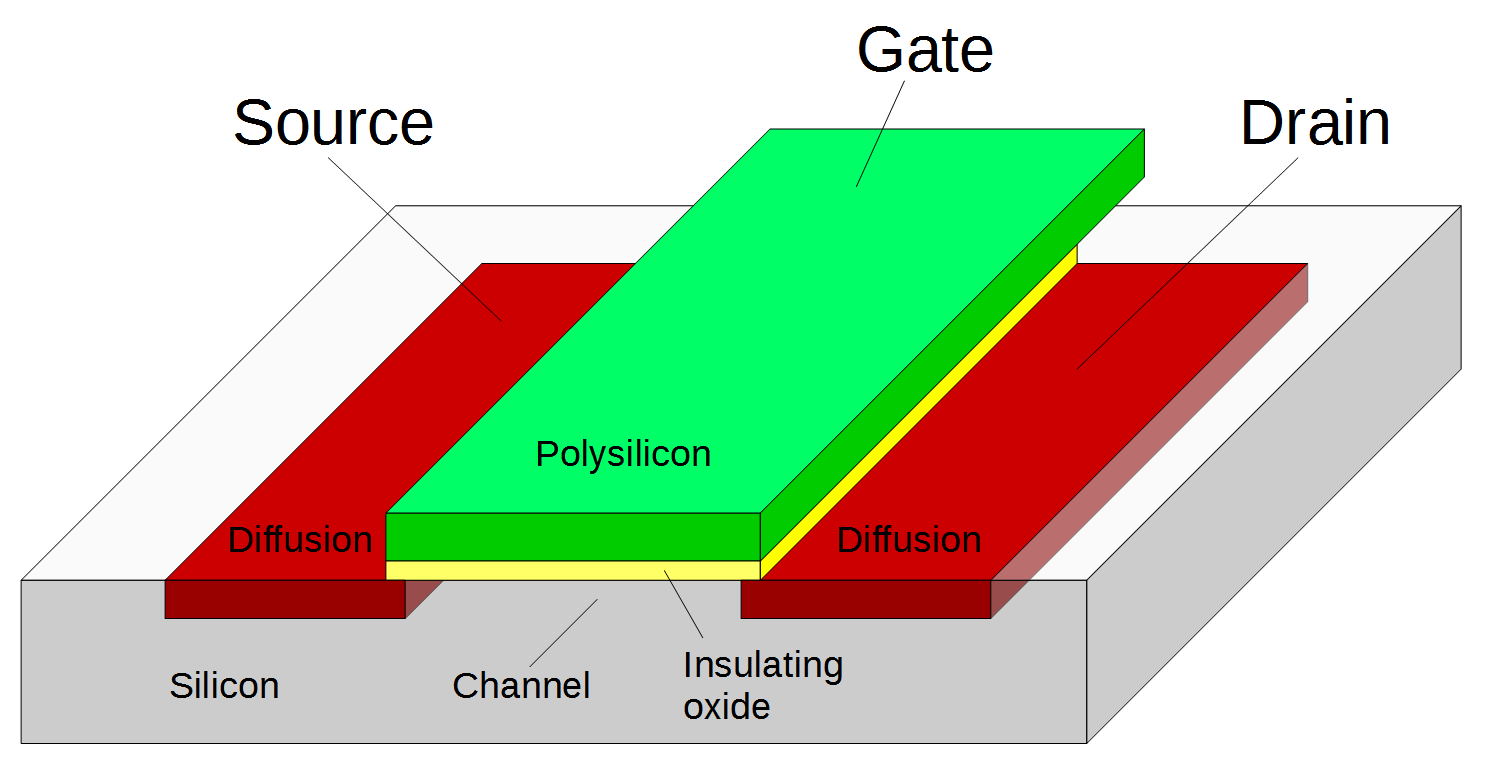

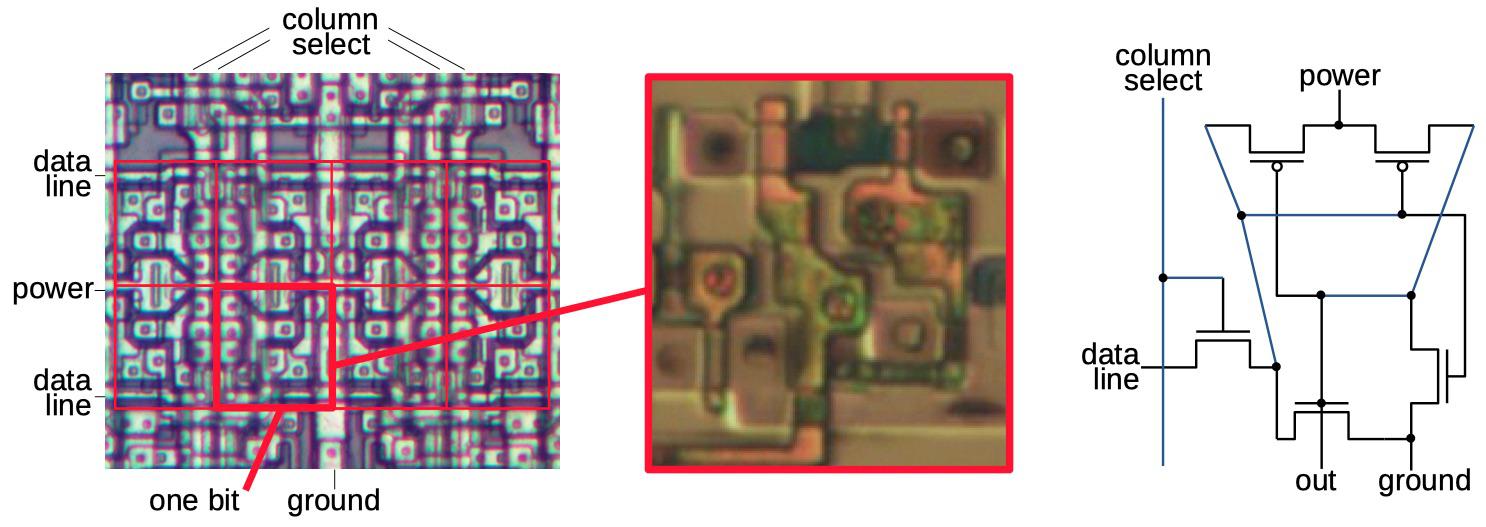

FPGA在由NMOS和PMOS晶体管构建的CMOS(CMOS)逻辑上实现。晶体管在FPGA中扮演两个主要角色。首先,逻辑元素由它们的组合形成。其次,晶体管被用作开关,信号通过该开关例如形成块之间的连接。担当此角色的晶体管称为直通晶体管。下图显示了MOSFET的基本结构。两部分硅掺杂有杂质,以形成漏极和源极。在它们之间的是一个栅极,该晶体管导通和截止晶体管,并控制漏极和源极之间的电流。百叶窗由一种称为多晶硅的特殊类型的硅制成,通过一层薄薄的氧化物与下面的硅绝缘。在其上方,有两层金属化层,可提供电路连接。

MOSFET的结构

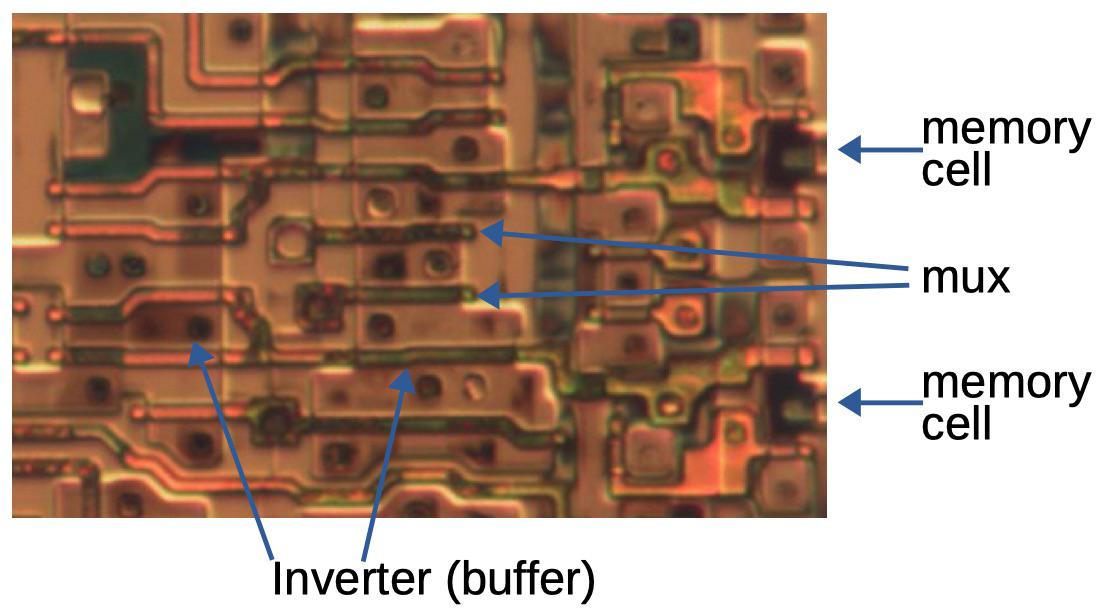

在晶体的照片中,我们可以在显微镜下观察晶体管的外观。多晶硅栅极是在两个硅掺杂区之间的蛇形线。圆圈是连接硅和金属层的通孔(在此照片中已除去)。

FPGA MOSFET

比特流和配置存储器

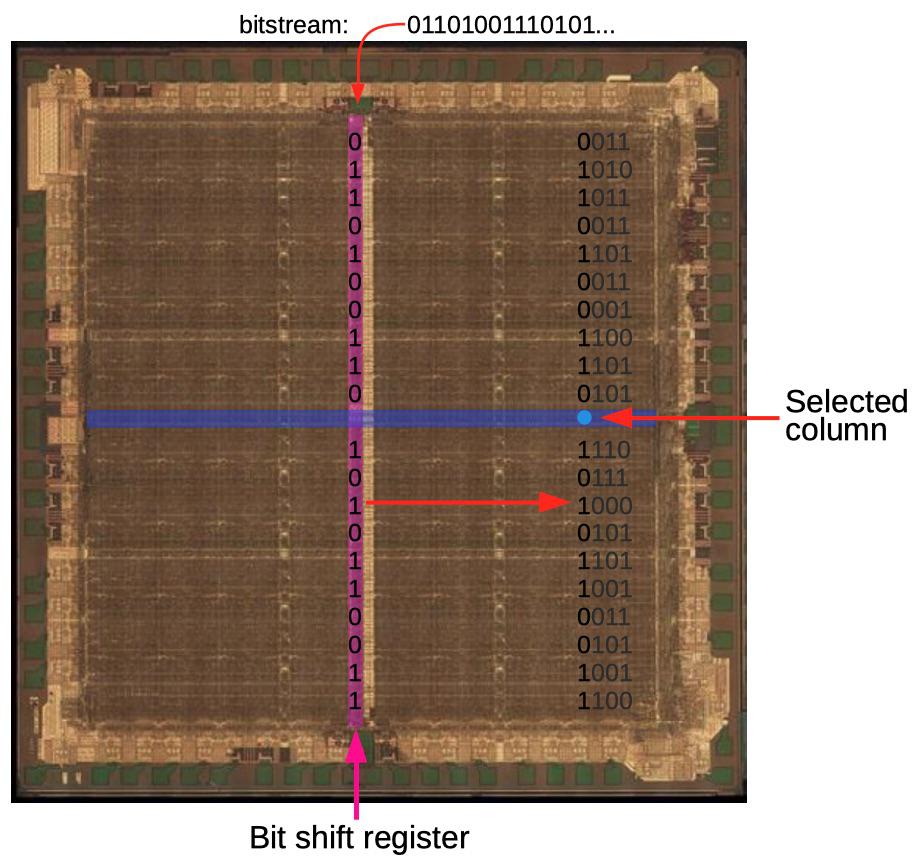

XC2064中的配置信息存储在配置存储位置中。 FPGA不为此使用块存储器,而是将配置存储器以160x71晶格的形式分布在整个晶体中,每个位紧挨着它控制的电路。下图显示了加载到FPGA中的配置比特流。比特流被加载到芯片中间(粉红色)的移位寄存器中。一旦将71位加载到移位寄存器中,列提取电路(蓝色)将选择所需的存储列,并且将这些位并行加载到该列中。然后,接下来的71位被加载到移位寄存器中,并选择左侧的下一列。对FPGA的所有160列重复此过程,并将整个位流加载到FPGA中。移位寄存器的使用消除了对大型存储器寻址电路的需求。

比特流如何加载到FPGA中。常规上显示位,但位的实际存储要密集得多。右边的三列已经加载,第四列正在加载。晶体的照片是从这里拍摄的:Siliconpr0n。

重要的是,比特流必须按照比特在文件中出现的顺序准确地分布在整个芯片上:比特流中的比特打包与它们在芯片上的物理位置相对应。如下所示,每个位都存储在FPGA控制的电路旁。因此,比特流文件格式直接由硬件电路的位置确定。例如,如果瓦片之间存在间隙,并且其中有缓冲区,则位流中将存在相同的间隙。比特流的结构不依赖于软件抽象,例如数据表或配置块中的字段。了解比特流需要以硬件而非软件的方式进行思考

比特流

, (.RBT) , .

, .

, .

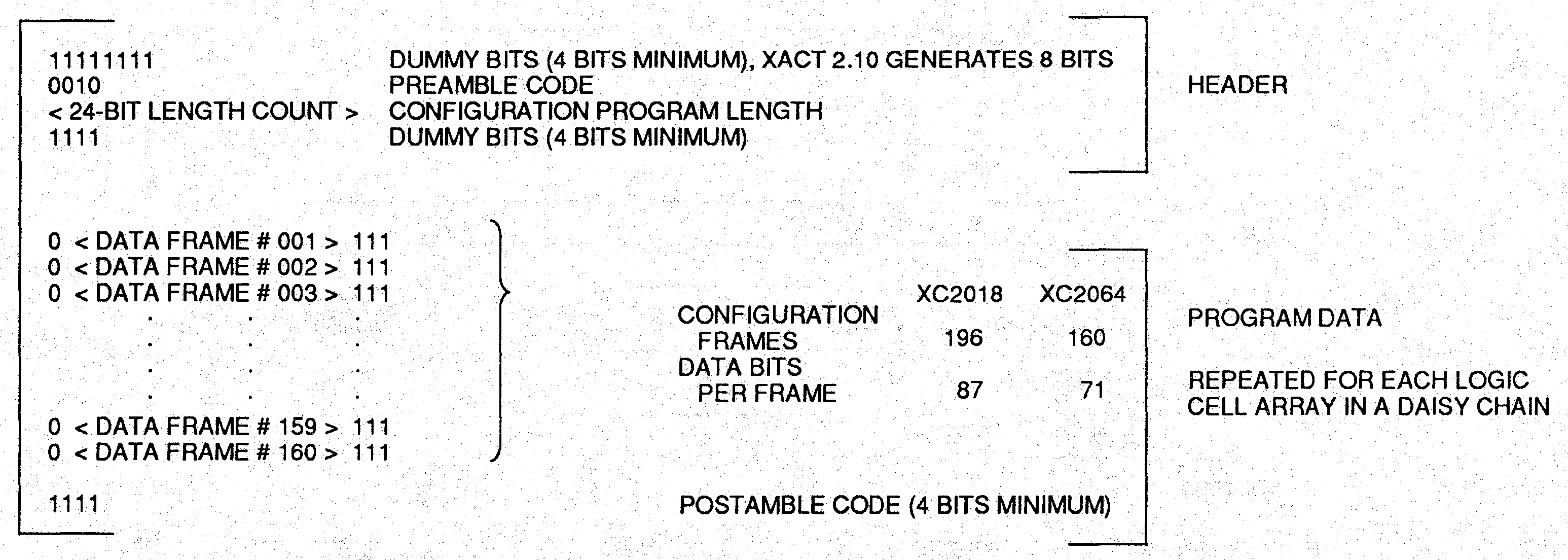

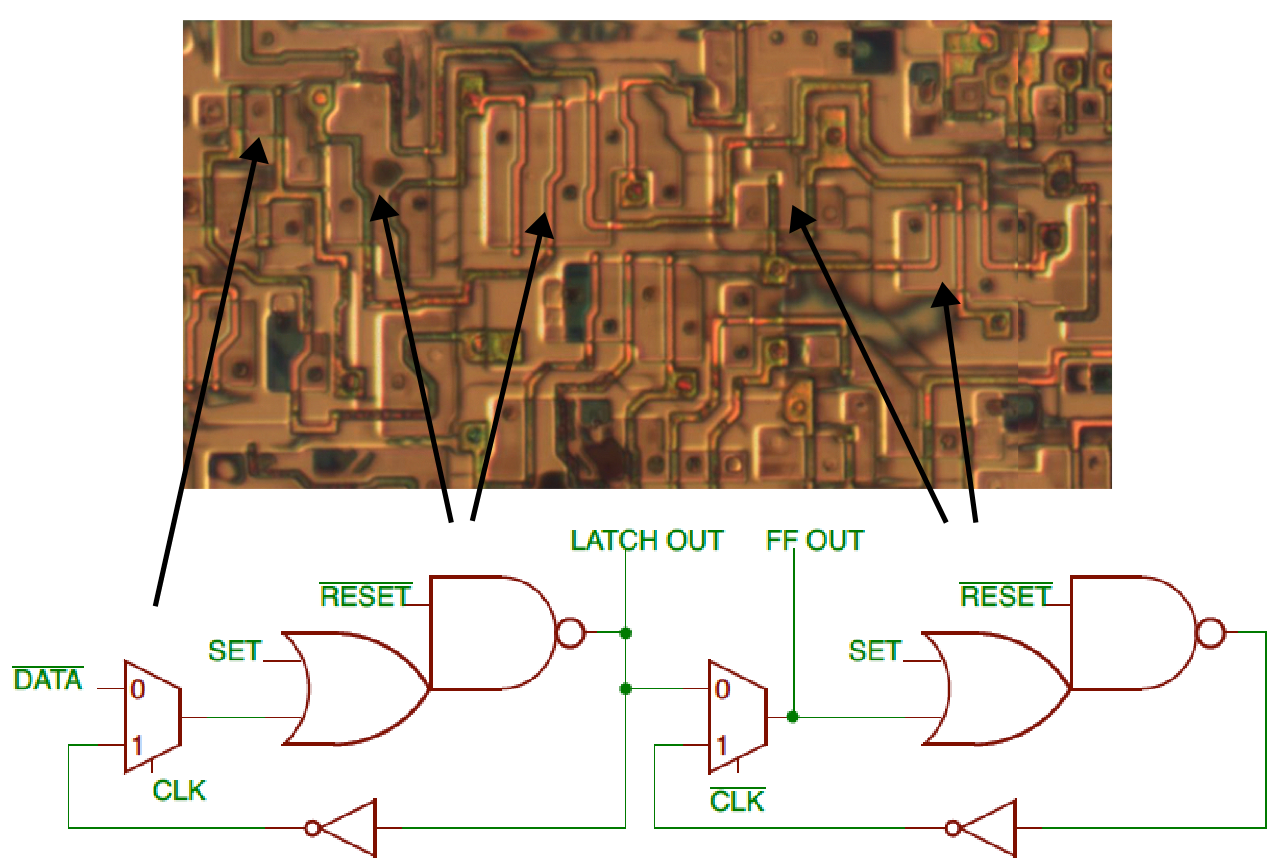

如下所示实现配置存储器的每一位。每个存储单元都包含两个以环路连接的反相器。这样的电路具有两个稳定状态,并且可以存储一位:上级反相器处于状态1,下级反相器处于状态0,反之亦然。要写入单元,左侧的传输晶体管被激活,传递信号。数据线上的信号简单地拉动逆变器,写入所需的位。(您也可以使用相同的行读取配置数据。)输出Q和反相Q控制FPGA中的特定功能,例如关闭互连,从查找表中检索某位或控制触发器。在大多数情况下,仅使用Q输出。

SRAM单元

(SRAM). , RAM, , , SRAM. , 5T SRAM.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

文档中的一位配置存储器图。

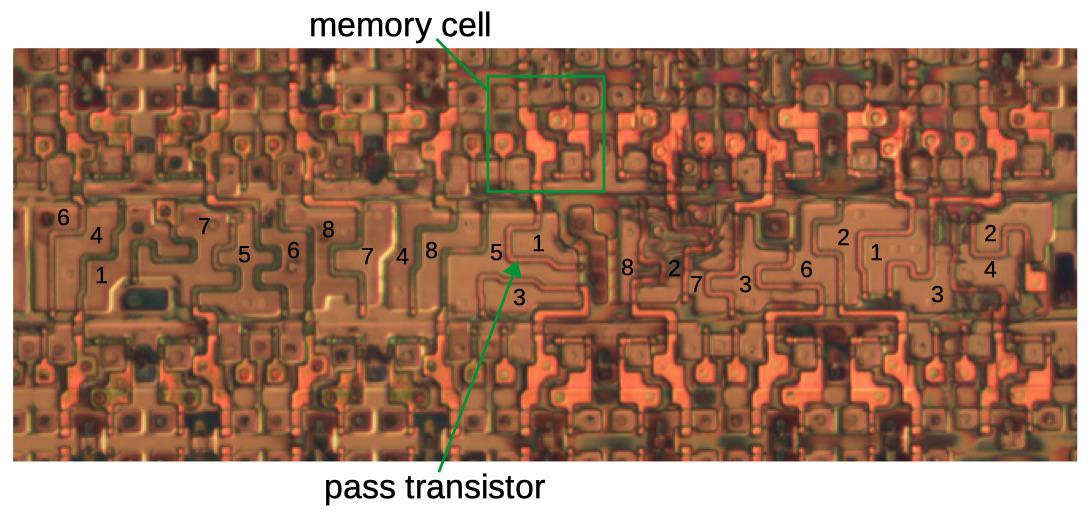

下图显示了存储单元的物理结构。左图显示了8个存储单元,其中一个高亮显示。每条水平数据线都连接到该行中的所有存储位置。每个列提取行选择该列中的所有存储位置,从而允许写入。中间照片显示了一个存储单元的硅和多晶硅部分。金属层已被去除以暴露下面的晶体管。金属化层连接晶体管,照片中的圆圈,这些是硅或多晶硅与金属之间的连接,过孔。该图显示了五个晶体管的连接方式,图中元件的位置与它们在照片中的位置相对应。两对晶体管构成CMOS反相器,左下方的直通晶体管提供对单元的访问。

, . — . , . . : siliconpr0n.

如前所述,FPGA使用查找表实现任意逻辑功能。下图显示了如何在XC2064中实现查找表。左侧的八个值存储在八个存储位置中。四个多路复用器根据输入A上的值选择每对值中的一个,如果A = 0,则选择较高的值,如果A = 1,则选择较低的值。然后,大型多路复用器根据信号B和C选择四个值之一。结果将是一个特定值,在这种情况下为A XOR B XOR C.如果将不同的值代入表中,我们可以执行任何逻辑功能。

查找表中的XOR实现。

每个多路复用器均通过直通晶体管实现。根据控制信号,通过晶体管之一被激活,将数据从输入传递到输出。下图显示了LUT链的一部分,其中两位被复用。右边是两个存储位置。每个位都经过反相器,被放大,然后穿过中间的多路复用器的直通晶体管,从而选择这些位之一。

实现LUT的网络视图。取自Siliconpr0n。

触发

每个CLB包含一个触发器,该触发器允许FPGA实现锁存器,状态机和其他有状态网络。下图显示了(有些不同)触发器实现。她使用以下方案。当时钟信号为零时,第一多路复用器将数据传递到第一锁存器,该锁存器存储该值。该位经过“或”门,“与非”门和反相器门后被反转两次,结果保持不变。此外,当时钟升至1时(请注意时钟是反相的),第二锁存器多路复用器从第一锁存器接收该位。该值是触发器的输出。当时钟信号设置为0时,辅助多路复用器通过锁存该位来闭合环路。因此,触发器对信号的边缘敏感,在时钟信号的上升沿锁存该值。置位和复位线设置并复位触发器。

. OR-NAND : siliconpr0n.

开关矩阵是重要的互连元件。每个开关有8个引脚(每侧两个),几乎可以任何方式连接它们。与单独的互连节点相比,信号可以更灵活地展开,拆分和相交。下图显示了四个CLB之间的互连网络的一部分(蓝色)。开关矩阵(绿色)可以通过右侧的任意组合连接。请注意,每个针脚可以连接5到7件的数量。例如,引脚1可连接到销3,而不是管脚2和4这使得基质几乎完全的,20间可能的连接,而不是28

从这里摘自:赛灵思可编程门阵列数据手册,图7b。

开关矩阵由受其上方和下方的存储单元控制的晶体管行构成。晶体管的两侧是开关矩阵的两个引脚,可以通过晶体管连接。因此,每个矩阵有20个控制位,每个图块两个矩阵给我们每个图块40个位。下图显示了一个存储单元,该存储单元连接到下面的晶体管的波浪形栅极。该晶体管提供引脚5和引脚1之间的连接。因此,位流中与该存储位置相对应的位控制引脚5和1之间的连接。类似地,其他存储单元及其相关晶体管控制其他连接。另请注意,这些连接的顺序不遵循任何特定的模式,因此,位流中的位与开关引脚之间的对应关系看起来是随机的。

开关矩阵

20 . 18 , .

实现8引线连接矩阵。硅区域由其相应引脚的编号指定。将对应的引线连接到晶体管的金属层已被去除。取自Siliconpr0n。

输入连接

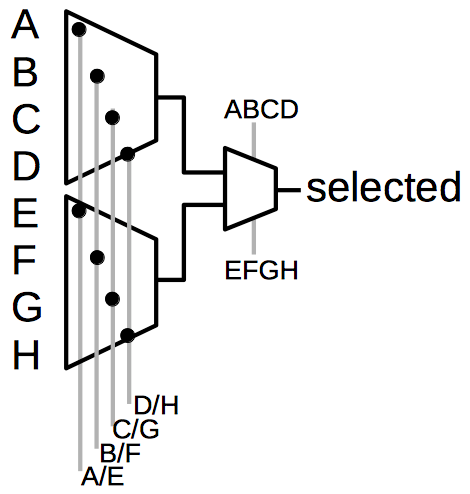

CLB输入使用不同的比特流编码方案,这由其硬件实现方式解释。在下图中,八个省略的节点是CLB的潜在输入,称为DD。只能将一个节点(最大)配置为输入,因为将两个信号连接到一个输入会将它们短路在一起。

输入选择。绿色圈出的八个输入是潜在的DD输入,只能选择其中之一。

所需的输入由多路复用器选择。一个简单的解决方案是使用具有三个控制位的8输入多路复用器,从8个信号中选择一个。另一个简单的解决方案是使用8个通过晶体管,每个晶体管都有自己的控制信号,其中一个选择所需的信号。但是,FPGA使用一种混合方法,在第一种情况下不需要解码器,但是需要5个控制信号,而不是第二种方法中的8个。

FPGA使用多路复用器选择八个输入之一。

上图显示了FPGA中使用的两层多路复用器。在第一阶段,控制信号之一被激活。在第二阶段,选择高信号或低信号并将其施加到输出。例如,假设将控制信号B / F施加到第一级,将ABCD施加到第二级,则输入B将是到达输出的唯一信号。也就是说,选择八个输入之一需要在位流中使用5位,并使用5个存储位置。

输入多路复用器CLB

CLB. EFGH ABCD, . -, CLB 6 10 , , . , , , , . , , 6 , . , , .

结论

XC2064使用各种高度优化的网络来实现逻辑块和网络互连。这些链需要紧密包装,以适合晶体。即便如此,XC2064还是一个非常大的芯片,比当时的微处理器还大,而且制造困难,成本高达数百美元。与现代FPGA相比,XC2064的单元数非常少,但这甚至是革命性的新产品线的开始。

有两个概念是理解XC2064比特流的关键。首先,FPGA是在64个图块的基础上实现的,这些图块是结合了逻辑块和互连的重复块。尽管FPGA被描述为具有被互连件包围的逻辑块,但是并不能以这种方式实现。第二个概念是比特流不基于任何抽象,它直接映射FPGA存储单元的二维打包。因此,只有在考虑FPGA的物理结构时,比特流才有意义。

注意

, XC2064 (. 11), CLB . , , 20% , . — -, . , . .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

我已经在Twitter上发布了我的最后一篇文章,所以关注kenshirriff。我也有一个RSS feed。感谢John McMaster,Tim Ansell和Philip Freidin的讨论。