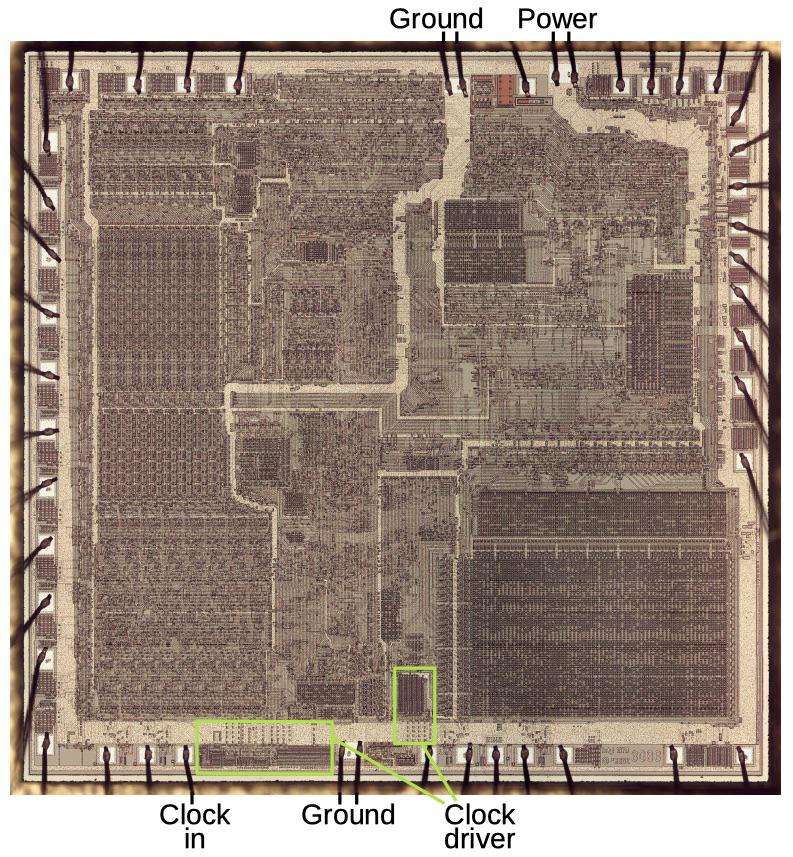

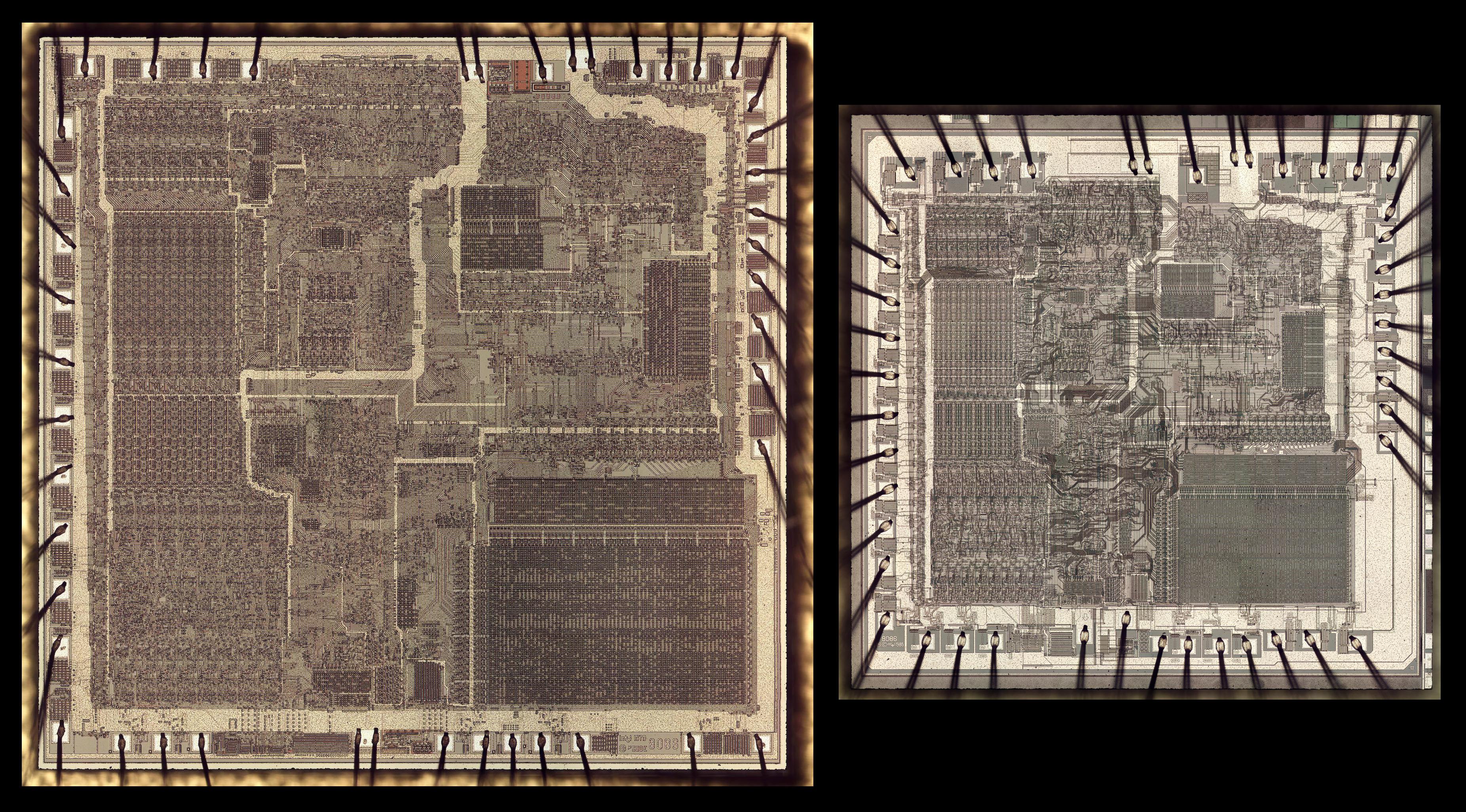

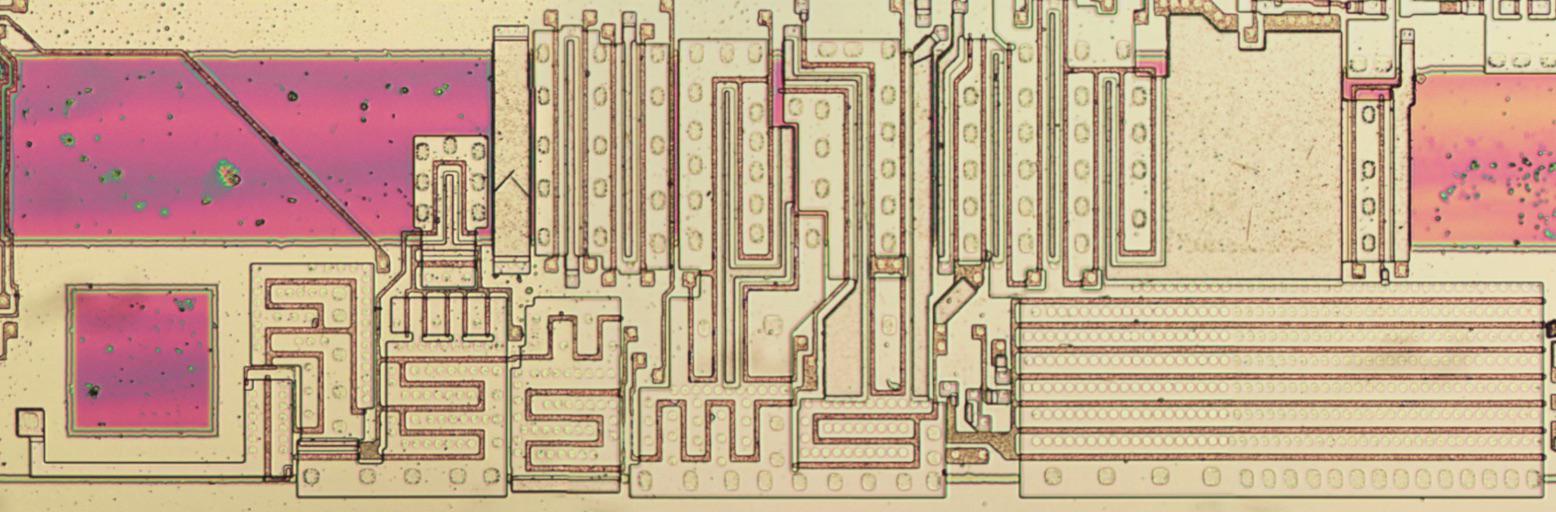

下图显示了在显微镜下的8086晶体。在芯片顶部可见金属层,在该金属层下隐藏了硅基板和带有导体的多晶硅层。沿着晶体外围的外部,一根细小的引线键合将晶体的焊盘连接到外部引脚。 8086的顶部有电源垫,顶部和底部有接地垫。它们中的每根都有两根用于焊接的焊丝,使受支持的电流增加了一倍。从电源和接地垫延伸出的宽金属路径可见。它们在整个芯片上分配功率。

8086晶体的照片,您可以在其中看到电源点(顶部)和接地触点(顶部和底部)。时钟电路位于底部。

8086中有两个内部时钟信号负责同步。外部振荡器通过下面的输入时钟垫将时钟信号馈送到8086。内部时钟发生器基于外部信号提供两个大电流时钟信号。请注意,时钟驱动器占用了芯片很大的空间。

在本文中,我将介绍8086如何在整个芯片上重定向能量和时钟信号,以及时钟电路如何生成必要的时钟脉冲。

电力调配

8086由三层组成,每层可容纳导体。由于金属的低电阻,顶部的金属层最适合此用途。在金属下方有一层导体多晶硅层,由特殊类型的硅组成。多晶硅的电阻高于金属的电阻,但仍可用于在芯片上传输信号。晶体管形成在硅衬底上。硅的电阻较高,因此仅用于短距离传输信号-例如,在门内部。

像8086这样的芯片中的功率分配是一个难题。由于其低电阻,金属层仍然是电源和地线唯一实用的层。芯片上几乎所有的栅极都必须提供电源和接地。而且,由于芯片只有一层金属层,因此电源和地线无法相交。

芯片上几乎所有的栅极都需要电源和接地,因为标准MOS栅极的下拉网络需要接地,而上拉电阻则需要电源。但是,也有一些例外。 8086使用动态逻辑门(尤其是在ALU中)来提高速度。这些门被同步信号向上吸引,因此它们不需要直接电源。 8086在馈通晶体管上还使用了多个XOR门,这些XOR门被输入信号下拉,因此它们不需要接地。

微代码ROM构成了芯片的很大一部分,不需要电源,仅需接地即可。这是因为ROM的每一行都实现为非常大的NOR门,而将其上拉的电源位于右侧。因此,尽管ROM似乎缺少电源连接,但所有ROM门都具有电源和接地。

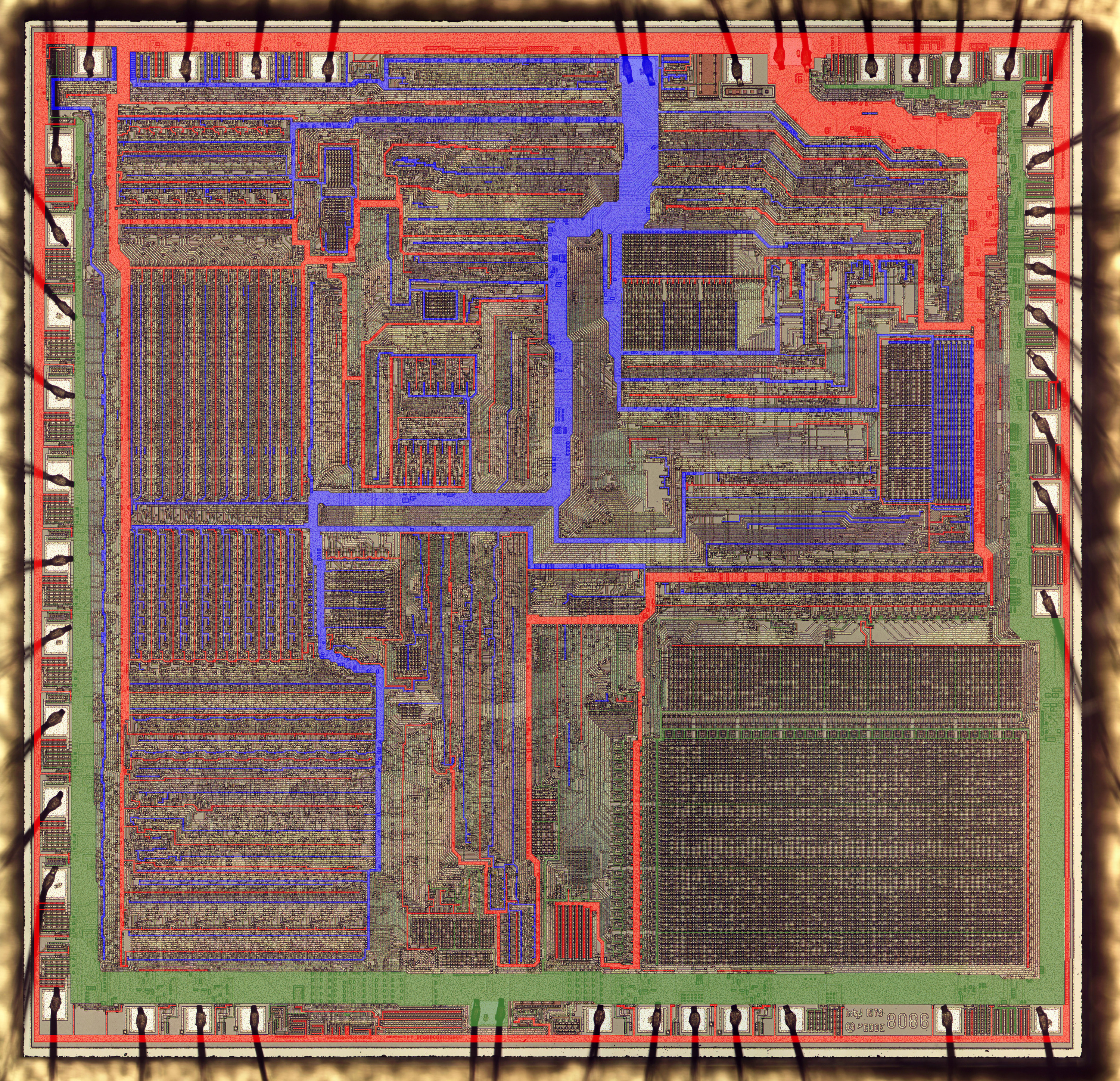

下图显示了8086中的金属导体。连接到顶部电源引脚的电源显示为红色。强大的食物分支向下和向右移动,然后分成许多分支。电源也沿整个芯片的边缘运行,为I / O引脚供电。

对于IC,通常会发生电源和地线位于芯片的相对角或相对侧的情况。这种布置使布线不相交的电源线和接地线更加容易。 8086在对角线相对的引脚上的电源和接地位置略有不同寻常,而第二个接地点更靠近电源引脚。电力网络和芯片上的平台像树一样分支。这些网络分支出来,就像缠绕的手指一样,到达芯片的所有部分。

芯片金属层上的电源(红色)和地线(蓝色,绿色)

有两个接地触点。蓝色标记的轨道连接到顶部的接地引脚,绿色标记的轨道连接到底部。蓝色标记的接地路径显示出一条粗细的分支,向下穿过芯片的中心,并以复杂的方式向各个方向分支。绿色通道沿着芯片的底部,左侧和右侧延伸,支持I / O引脚并连接到右下方的微代码ROM。

远离电源并靠近端点,电源线变得更细,电流减小。可以在下面的地址和数据引脚的电源导线中看到。在触点下方的左侧,接地导体非常宽,但逐渐变窄,向右移动。换句话说,在左侧,导体必须从所有触点传导电流,在最右侧,只能从一个触点传导电流。

地址和数据引脚到地的连接越来越薄(芯片的左侧旋转了90°)。

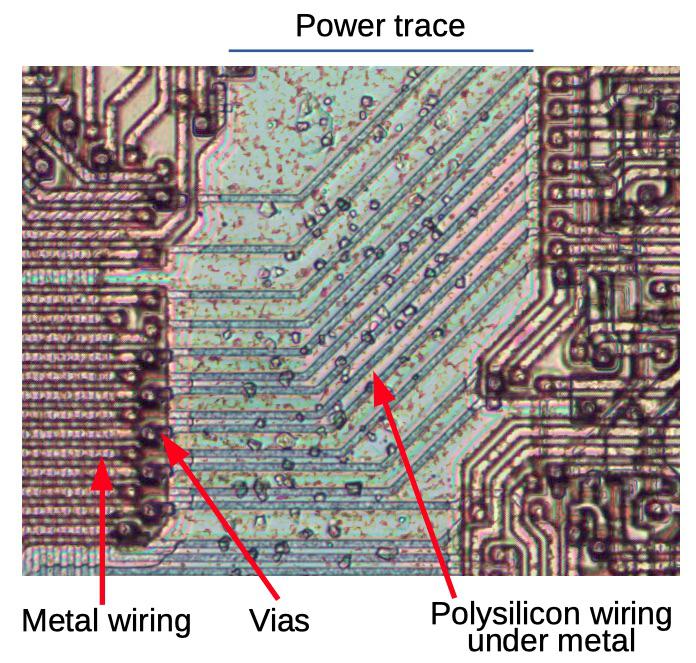

金属层用于承载许多信号,而不仅仅是电源和地。由于其低阻抗,它是最佳的信号传输层。然而,电力和接地导体的广泛使用限制了金属层的能力。为了避免交叉,金属层上的大多数信号路径与电源路径平行。下面的多晶硅层用于垂直信号传输。但是,如果金属导体需要越过电源或接地线会发生什么情况?解决方法是从底部[crossunder]绘制它。信号下降到多晶硅水平,穿过轨道,然后上升回去,如下所示。

在许多情况下,不仅要与食物一起使用这种底部通道。但是,最常见的是营养。通常,金属导体用于在一个方向上传输信号,而多晶硅导体用于在垂直方向上传输信号。这些方向在芯片上的不同位置会发生变化,并取决于信号传输的主要方向。因此,在大多数情况下,信号不受阻碍地传播。但是,它们常常不得不从一层跳到另一层。

金属层上的信号通过多晶硅层从下方穿过供电路径

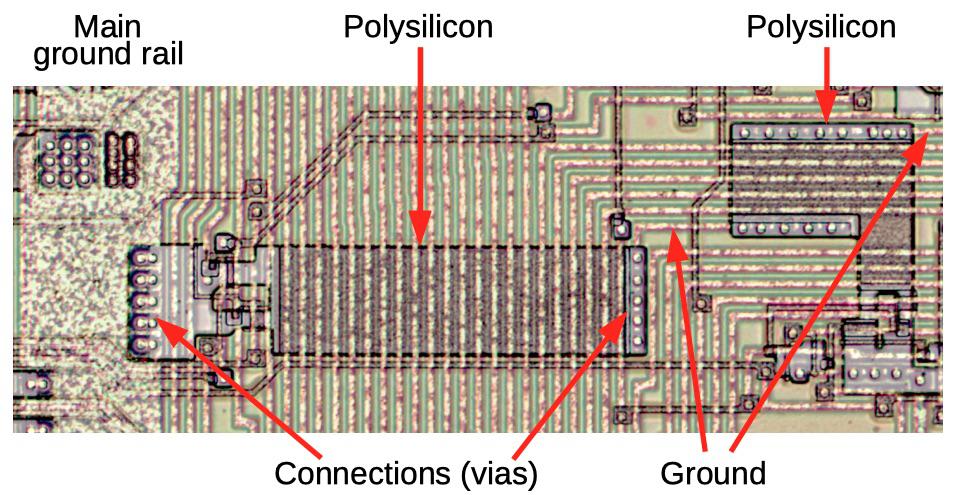

如果电源和地线几乎全部路由到金属层,则该电路会在几个地方断开,并且在其下方延伸的走线可用于供电。这种情况更多地发生在磁道的最后部分,此时电流已经很低。下图显示了一个示例-地面使用多晶硅导体从金属层的底部穿过两次。为了降低电阻,这些旁路路径要比信号路径宽得多,并且同时使用硅和多晶硅。小圆圈穿过金属和多晶硅层之间的接触。

复合照片显示接地旁路路径在信号路径下穿过多晶硅。

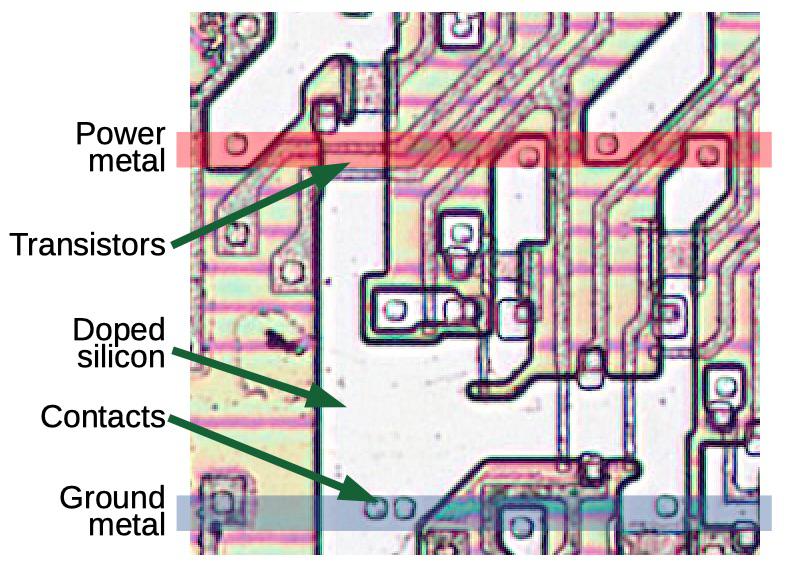

硅层在电源接线中起次要作用。特别是,许多闸门被拉伸以从另一侧到达电源和地面。下图显示了8086栅极,请注意大面积的掺杂硅(白色)被拉出并到达地面和电源轨。仅一小部分硅被用于晶体管,其他所有东西似乎都在浪费空间。但是,这些空的硅部分将栅极连接到提供电源和接地的金属导体。由于硅具有较高的电阻,因此需要使用较大的面积,并且接点本身会延伸很短的距离。

掺杂硅制成的栅极可以加长以达到电源和接地轨。对于这张照片,金属层已被去除。

在对8086进行更新并缩小之后,它还有其他电源接线问题。随着制造技术的改进,英特尔缩放了晶体,使电路保持不变,但按比例缩小了晶体。不幸的是,减小电源走线的尺寸也会减小最大电流。为了解决这个问题,增强了芯片周边的电源路径,并减少了内部电路和布线。可以在下面的照片中看到-例如,较小的8086的右下角有更多的电源轨道。

8086的两个版本具有相同的比例。右边的水晶是后继版本,尺寸减小了。

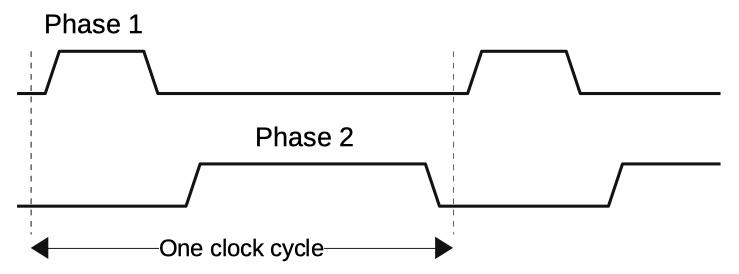

几乎所有计算机都使用时钟信号来控制处理器的时序。像许多微处理器一样,8086在内部使用两相时钟驱动器。两相时钟驱动器有两个时钟-当第一个为高电平时,第二个为低电平,反之亦然,如下所示。一些电路通过第一个同步信号打开,而另一些则通过第二个同步信号打开。 8086的工作方案表明,同步信号的两个相位之间没有重叠,并且它们的不对称性-当一个同步信号变低而第二个同步信号上升时的时刻之间存在间隙。

两相时钟驱动器由两个极性相反的时钟信号组成。

尽管几乎所有计算机都使用时钟信号进行同步,IAS体系结构(在1950年代流行)是异步的,无需时钟信号即可运行。取而代之的是,每个电路完成后都会向下一个发送脉冲,从而触发下一步。 1950年代初期,许多计算机都基于这种体系结构,包括CYCLONE,ILLIAC,JOHNNAC,MANIAC,SEAC和IBM701。对异步计算的可能性的研究仍在继续,但同步系统无疑占主导地位。

处理器除其他外,使用时钟信号来防止电路中不必要的反馈。例如,考虑一个软件计数器,其链递增其值并将其反馈给计数器。您不希望新值不断增加。

一种方法是使用触发器,当信号从低到高时会更新值。然后,计数器将仅在需要的时间更新。但是,利用两相同步信号,可以在电平敏感的锁存器上制作该电路,其设计比对信号变化敏感的触发器要简单得多。当第一个同步信号为高电平时,梯级的前半部分接收输入值并执行逻辑计算。当第二个同步信号为高电平时,链的第二部分从上半部分接收结果并执行所有必要的计算,第一部分被阻塞。关键是一次只能更新链的一半,这可以防止不必要的反馈。

8086具有严格的输入时钟要求,该时间必须是三分之一的时间。通常,8086由8284芯片和石英晶体产生。芯片将输入时钟信号除以3,以提供8086所需的33%时钟占空比。

在现代处理器中,时钟信号的布局非常复杂,因为信号必须同时传播到芯片的所有部分。现代处理器使用时钟路径的层次结构,平衡每个路径的传播时间,并经常为每个路径提供单独的缓冲。相比之下,8086的时钟信号布局非常简单,因为其5-10 MHz的时钟频率比现代处理器的时钟频率低几个数量级。在这些相对较低的频率下,路径长度并不重要,因此8086的时钟脉冲可以跟随绕组路径。

由于8086使用动态逻辑,因此其最小时钟速度也为2 MHz。如果频率较低,则在重新充电之前存在电荷泄漏的风险,这可能会导致故障。从调试的角度来看,最小时钟频率是不方便的,因为不可能减慢或停止时钟信号。

8086中的同步路径。绿色是第一个同步,红色是第二个,相位相反

上图显示了8086的时钟路径,阶段1为绿色,阶段2为红色。在芯片的底部,时钟驱动器电路显示为大斑点。从那里,同步信号在整个芯片上分支出来。在大多数情况下,这两个时钟阶段是并行运行的,与电源和地相反的两个分支相反。

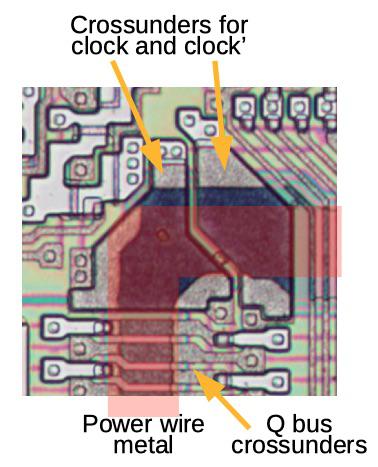

由于同步信号传播到芯片的所有部分,因此与常规信号相比,它们需要的电流要大得多,因此,它们大多被路由到金属层。当同步信号需要越过电轨时,它们会在其下方通过,如下所示。请注意,同步解决方法在形状上是不规则的-它们远远超过其他信号(例如Q总线)的解决方法。

电源的旁路路径非常大。 Q总线(将命令从命令队列传输到解码器)的数量要少得多。

为了提供大电流同步信号,其整形电路建立在大型晶体管上。下图将这些晶体管之一与典型的逻辑晶体管进行了比较。驱动晶体管的尺寸约为300倍,因此能够提供300倍的电流。该晶体管由10个并联放置的晶体管组成-10条垂直多晶硅线形成10条栅极。每个同步信号由一对大型晶体管产生,其中一个将其上拉,另一个将其下拉。

时钟驱动器中的大晶体管与相邻逻辑晶体管相比

下图显示了同步脉冲发生器的示意图。该电路将外部时钟信号分为两相,确保它们不重叠并放大。左侧的粉红色正方形是用于外部时钟驱动器的平台。信号通过一系列晶体管,这些晶体管终止于右侧的大型驱动器晶体管。棕色导体是形成栅极的多晶硅。许多晶体管具有Z字形栅极,因此大型晶体管可容纳在较小的空间中。

片内时钟驱动器电路。金属层已被去除。大晶体管可见。外部同步输入引脚-左侧为粉红色正方形。

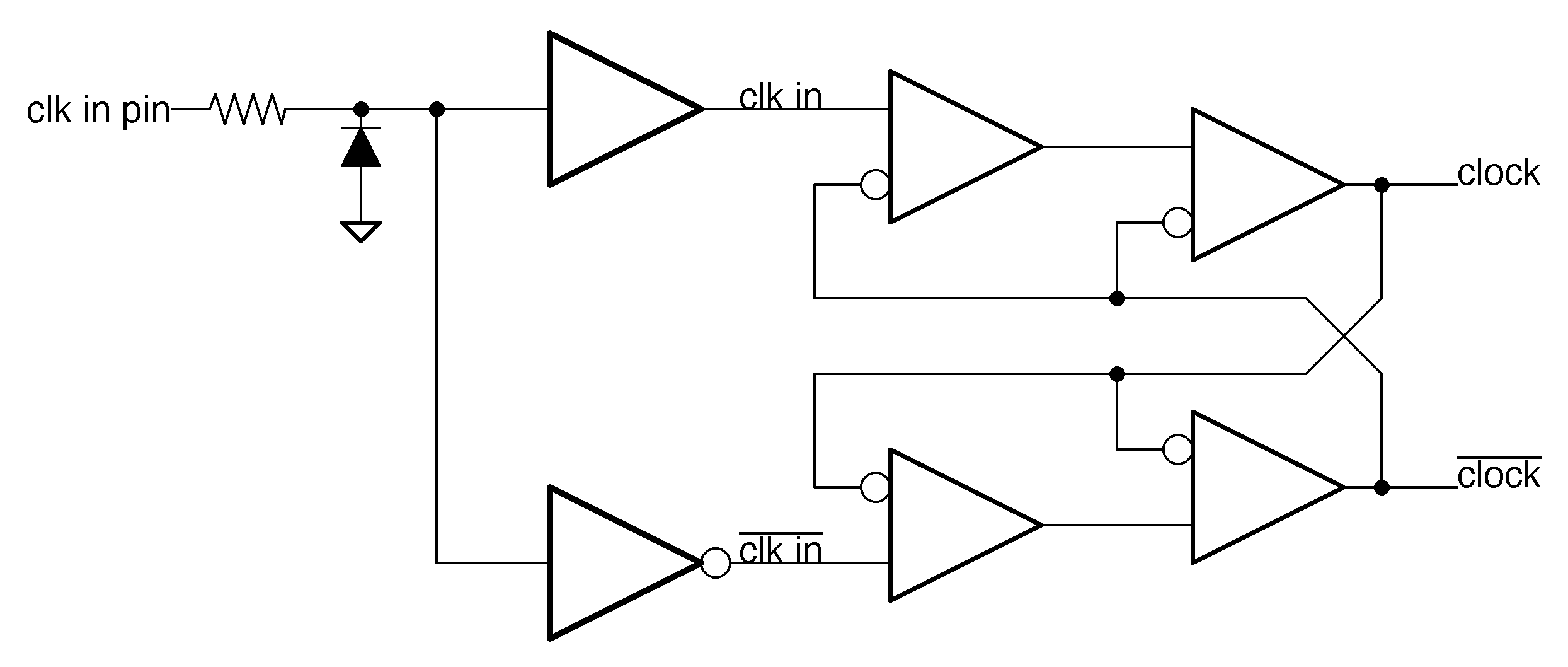

下面是时钟发生器的略微简化的示意图。三角形是由两个或三个晶体管制成的高电流驱动器。反相输入(圆圈)将输出下拉。在输入同步引脚的左侧,有一个小的电阻器和二极管来保护它(就像其他输入引脚一样)。然后将同步信号分为反相(顶部)和反相(底部)。

8086时钟发生器的简化示意图

附加电路可防止同步信号重叠:当一个信号为高电平时,这通过反相输入导致第二个信号为低电平。为了了解其工作原理,让我们从当时钟输入引脚上的信号为高电平时开始。 clk in和clock的信号为高,而^ clk in和^ clock的信号为低。现在,假设进入clk in的输入信号变低,这导致进入clk in的信号下降,而进入^ clk in ^上升。但是,直到clock下降,^ clock ^的输出才能上升。之后,^中的信号^ clk将通过较低的驱动器,在两个门延迟之后将^ clock ^向上拉。关键是时钟和时钟^^不能同时切换。一个变低之后,另一个变高之前有一个延迟。结果,我们得到了不重叠的同步信号。

这是一个非常粗略的描述-特别是,我不确定一个晶体管将一个信号上拉而另一个晶体管将同一信号拉低时会发生什么。该过程的精确模拟将取决于两个晶体管的相对大小。

结论

8086使用有趣的电源布局,但是现代处理器的运行水平却完全不同。如果8086需要350mA电流,那么现代处理器可能需要超过100A的电流。8086使用其40支脚中的3根作为电源和接地。现代的Intel Core i5处理器具有128个电源引脚和377个接地(总共1151个引脚中)。尽管现代芯片中的众多金属层解决了8086的布线问题,但它们带来了新的复杂性,例如将芯片划分为功率部分,从而可以禁用未使用的部分。

在具有几千兆赫兹速度的现代处理器中,同步信号的接线要复杂得多,因为额外的毫米磁道会对同步信号产生负面影响。为了解决这些问题,现代处理器使用诸如H树或时钟分配网络之类的东西,而不是像8086这样的分支轨迹。尽管8086具有简单的两相时钟生成电路,但现代处理器通常使用锁相环来合成时钟信号。 ,并且遍布整个芯片的许多电路提供并控制时钟信号。但是,尽管8086比现代处理器要简单得多,但它包含许多有趣的电路示例。