8086具有80多个锁存器。其中一些存储AD引脚(地址/数据)或控制引脚的值。其他的则存储微码和微码的当前地址,以及微码例程的返回地址。第三个存储源和输出命令寄存器的位,以及命令的ALU操作。许多存储内部状态的状态,我仍然了解。

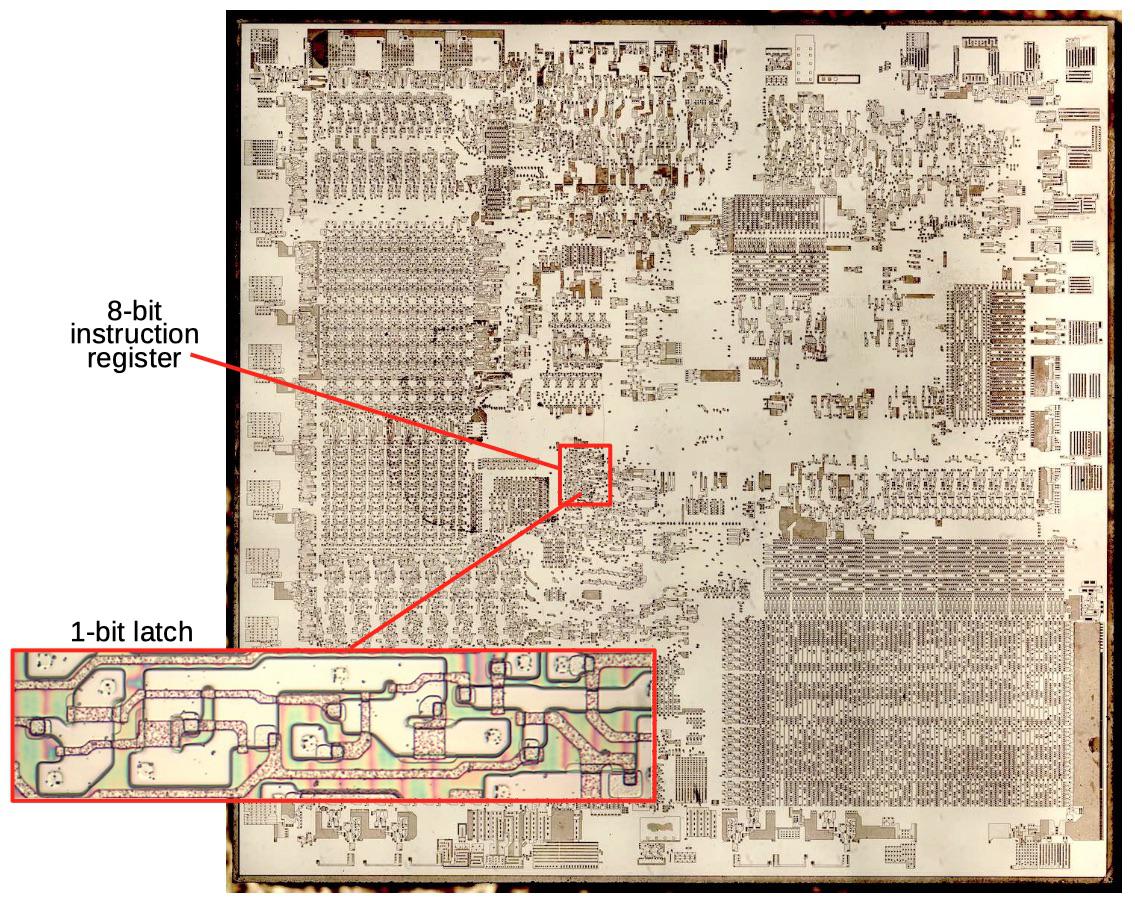

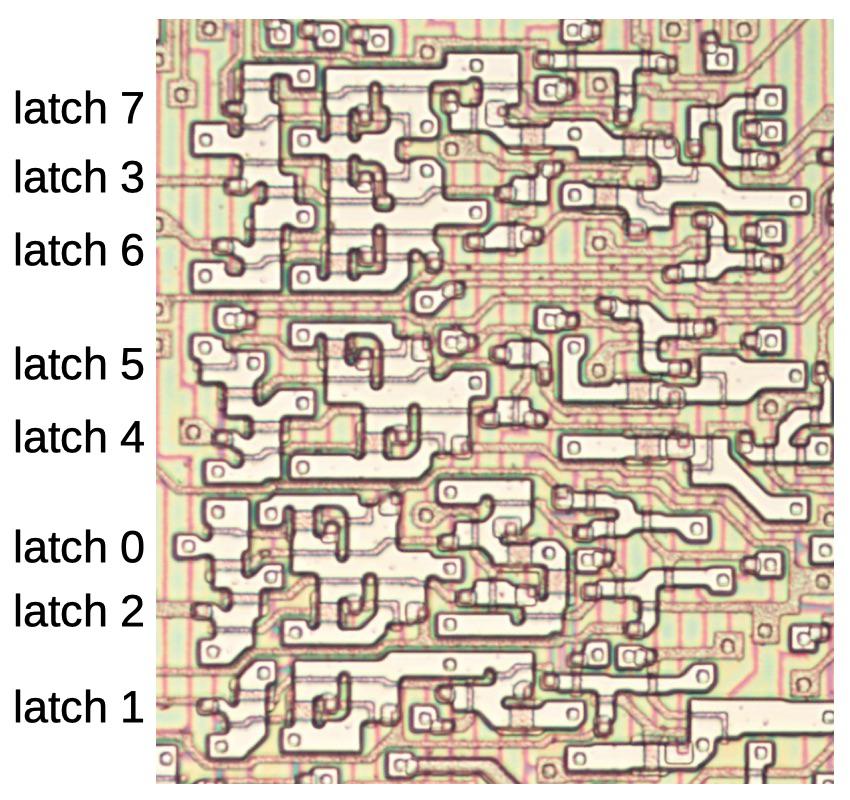

显示8位指令寄存器

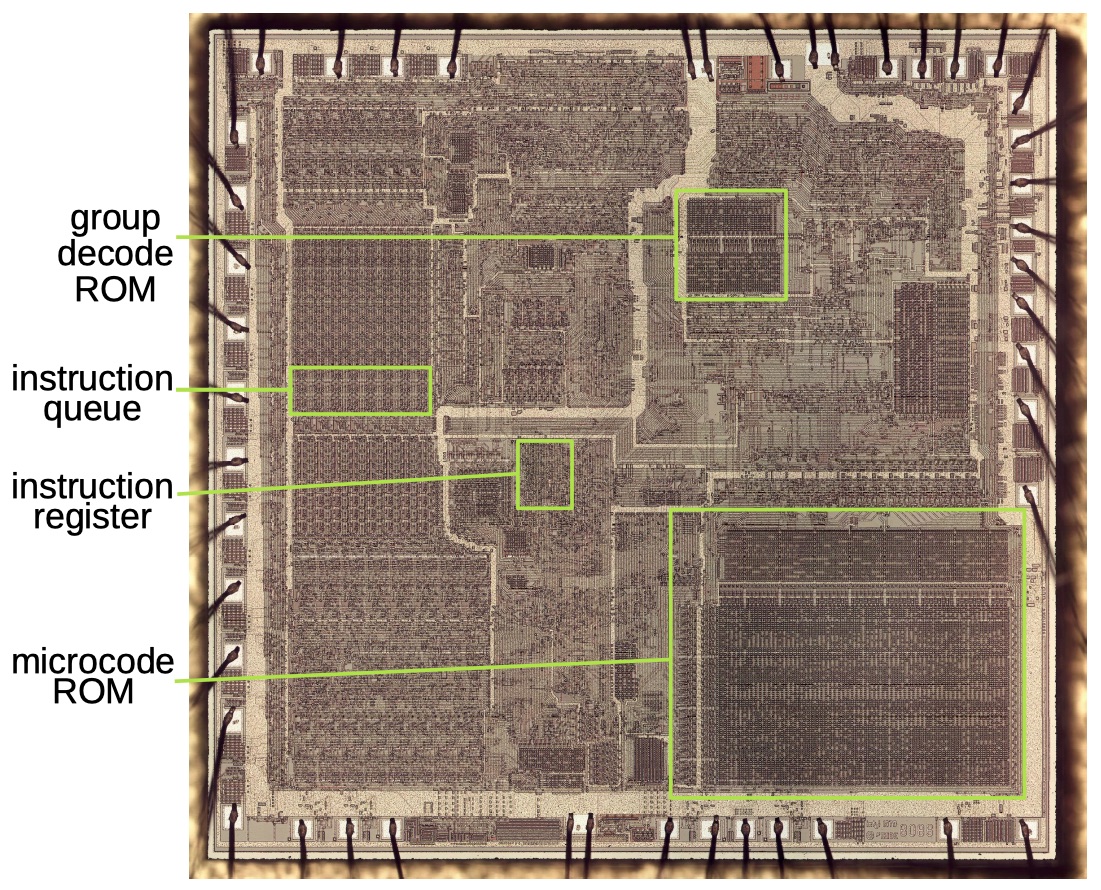

的晶体86上面的照片显示了在显微镜下的8086硅芯片。我删除了金属和多晶硅层,以便可以看到晶体管-总共约29,000。分配的区域包含一个8位命令缓冲区,由八个锁存器组成。1978年的处理器仍然足够简单,以至于单个8位寄存器占用相对较大的面积。放大图显示组成单个锁存器的硅和晶体管。

动态锁存器如何工作

锁存器是8086的最重要元素之一,因为锁存器可跟踪处理器的工作情况。闩锁可以通过不同的方式完成; 8086使用一种称为动态锁存器的紧凑电路。动态锁存器依赖于两相时钟发生器的操作,该时钟发生器通常用于控制那个时代的微处理器。两相时钟生成两个时钟信号,这些信号依次激活。在第一阶段,主时钟为高电平,伴随的时钟为低电平。然后他们改变了地方。以时钟频率(例如5 MHz)重复该周期。

许多微处理器使用“与非”门形成RS触发器。 RS触发器通常比动态锁存器占用更多的空间,尤其是在添加了附加电路以保持时钟频率的情况下。 D触发器(延迟触发器)也很流行,但它们变得更加复杂,并使用六个门。在许多情况下,通过晶体管就足够了;它可以存储一个时钟周期的值,但不提供长期存储。

始终为处理器选择最高的时钟速度。第一个8086的工作频率高达5 MHz,后来的8086-1的工作频率高达10 MHz。但是,由于使用了动态逻辑,因此8086还具有最低时钟频率:2 MHz。如果时钟发生器运行速度较慢,则存在在电路访问之前导体中电荷泄漏的风险,从而导致错误。

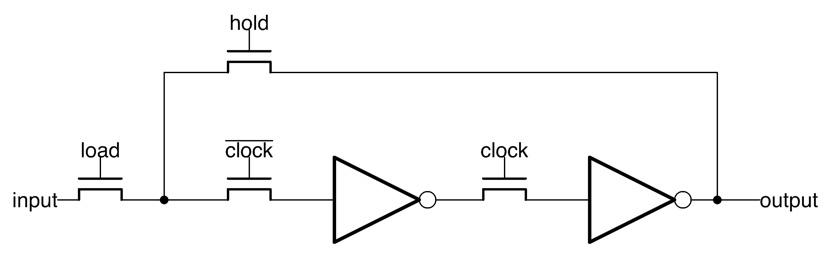

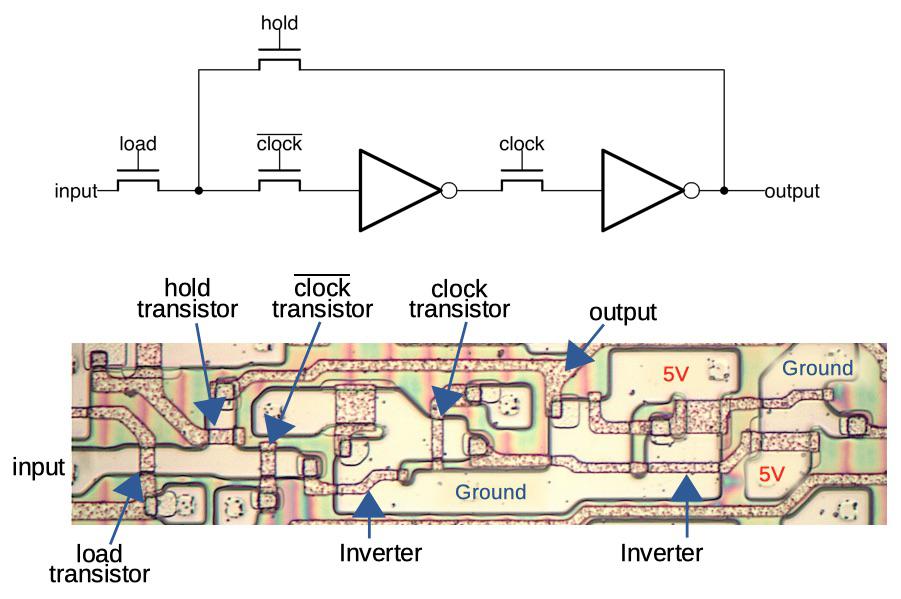

8086处理器中的锁存器由四个传输晶体管和两个反相器组成。锁存器以间歇时钟信号运行。

上图显示了一个典型的8086锁存器,它由两个反相器和几个传输晶体管组成。就我们的目的而言,直通晶体管可以看作是一个开关:如果1到达栅极,则晶体管会进一步传输信号。如果为0,则晶体管阻塞信号。传输晶体管由几个信号控制:负载,将一个位加载到锁存器中; hold(保持),保持现有位值;第一阶段的时钟和第二阶段的时钟反相。

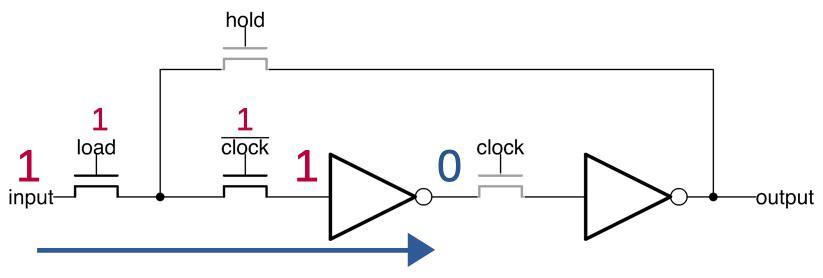

下图显示了如何将值(在这种情况下为1)加载到锁存器中。负载信号上升,使输入信号(1)通过晶体管。自时钟信号高电平时,信号通过第二个晶体管到达反相器,该反相器输出0。这时,第三个(时钟)晶体管阻止该信号。

当负载信号为高电平时,输入信号被加载到锁存器中。

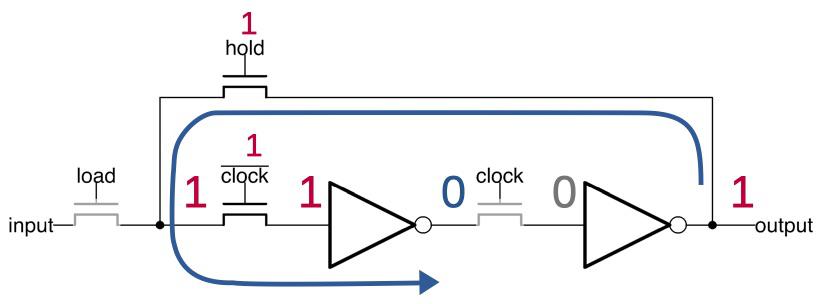

在下一个时钟相位中,时钟信号变为高电平,使0信号到达第二反相器,该反相器输出1.由于保持信号为高电平,该信号返回,但被时钟晶体管阻塞。...使该电路动态的原因是当前没有输入信号被发送到第一逆变器。由于电路的电容,其输入保持为1(以灰色显示)。总有一天,这种电荷会泄漏,其值会丢失,但是在那之前,将发生时钟脉冲发生器的新切换。

当时钟信号变高时,该值通过第二个反相器。通过电路的电容来保持对第一反相器的输入(灰色)。

切换时钟发生器的状态后,第二个反相器的输入将提供电路容量(见下文)。信号返回,对第一个逆变器的输入进行充电和更新。在随后的时钟上,锁存器将在此模式与前一个模式之间切换,从而保持存储的值并保持输出稳定。

锁存器操作的关键是两个反相器的存在,它们使输出信号保持稳定。奇数数量的反相器会引起振荡-8086电荷泵使用此功能,另外,一对反相器使用一组8086寄存器存储位。但是,在一组寄存器中,两个反相器是直接连接的,而没有时钟驱动的传输晶体管,这会导致结构更紧凑但难以管理。

当时钟信号为高电平时,该值通过第一反相器。

在硅中实现

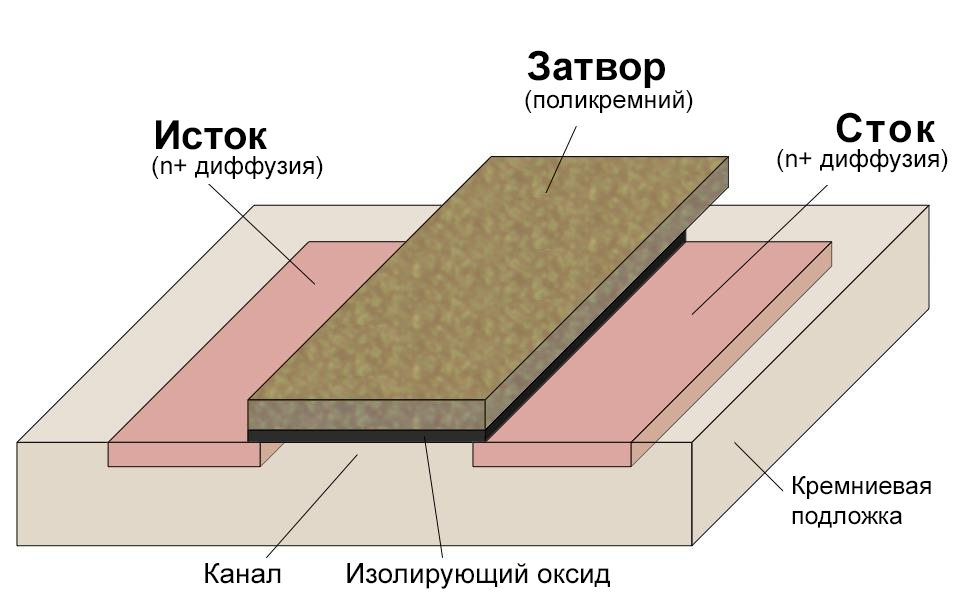

那个时代的8086和其他处理器都基于N-MOS晶体管。它们由硅衬底制成,在掺杂过程中,向其中添加了砷或硼杂质以形成晶体管。在硅的顶部是多晶硅,它形成了晶体管的栅极和将所有组件连接在一起的导体。另一层金属提供了额外的导电连接。相比之下,现代处理器使用CMOS技术(N-MOS和P-MOS技术的组合),并且具有多个金属导电层。

如何在IC中实现N-MOS晶体管(MOS结构)

上图显示了晶体管的结构。可以将晶体管视为允许电流从一个部分(源极)流到另一部分(漏极)的开关。晶体管由特殊类型的硅-多晶硅制成的栅极驱动。向栅极施加电压可使电流在源极和漏极之间流动,同时将栅极拉至0 V会阻止电流。栅极通过绝缘氧化物层与硅隔离-因此,栅极就像电容器一样工作,如在动态锁存器示例中所见。

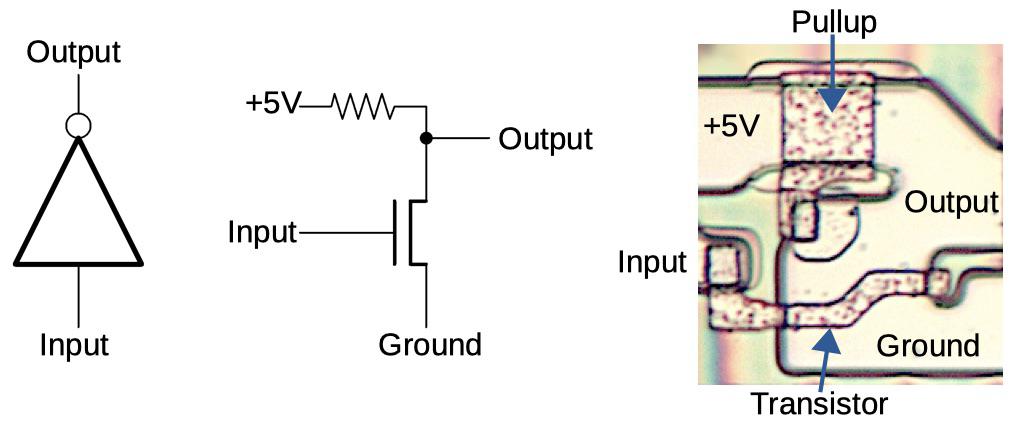

反相器(以下)由N-MOS晶体管和电阻组成。当信号为低电平时,晶体管截止,因此上拉电阻器将输出信号上拉。当信号为高电平时,晶体管导通,将输出接地,并拉低输出。因此,电路将输入信号反相。

N-MOS栅极中的上拉电阻是使用特殊类型的晶体管实现的。耗尽型晶体管的工作原理类似于电阻,但占用的空间较小,效率更高。

该图显示了如何由晶体管和电阻器制成反相器。照片显示了该电路是如何在芯片上实现的。金属层已被去除以暴露多晶硅和硅。

右图显示了8086在物理上如何实现逆变器。淡黄色区域是带有杂质的导电硅,斑点区域在顶部是多晶硅。在多晶硅与掺杂的硅相交的地方制造晶体管。多晶硅形成晶体管的栅极,两侧的硅部分提供晶体管的源极和漏极。一个大的多晶硅矩形在+ 5V和输出之间形成一个上拉电阻。您可以将这些物理结构的结构与图表进行比较。

下图显示了芯片上锁存器的实现。标有一个直通晶体管和两个反相器;以上说明了第一逆变器。多晶硅导体将组件彼此连接。金属层提供了其他连接(已为照片移除)。晶体管形状复杂,可以最有效地利用空间。

8086处理器中闩锁的显微照片除去了带有导体的金属层,但其痕迹以红色垂直线的形式可见。照片旋转180°以适合布局。

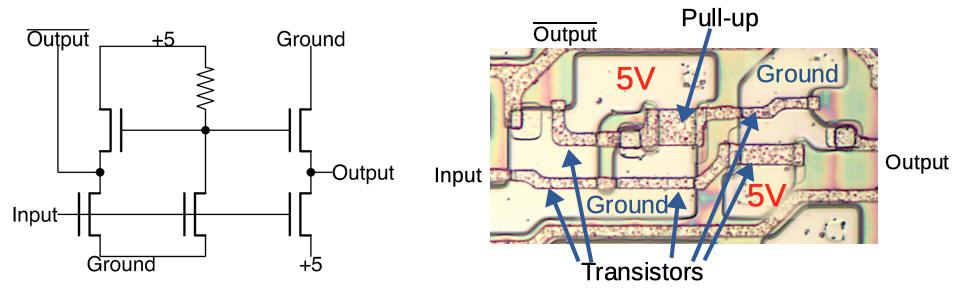

锁存器使用图中未标记的输出缓冲器为输出和反相输出提供大电流信号。这些缓冲器的名字叫“超级缓冲器”,因为它们提供的电流比典型的N-MOS反相器高得多。 N-MOS逆变器的问题在于,驱动某些高容量电路时,它运行缓慢。由于超级缓冲区提供了更多的电流,因此它可以更快地切换信号。它通过用提供更多电流的晶体管代替上拉电阻来实现此目的。缺点是上拉晶体管需要反相器才能工作,因此超级缓冲电路更加复杂。因此,仅在需要时才使用超级缓冲区-通常是在向多个门发送信号或驱动长总线时。

超级缓冲器的8086锁存器实现,请注意+5 V和接地连接移到了最右边的晶体管。

上图显示了8086锁存器超级缓冲器的示意图,与传统的超级缓冲器不同,它具有反相和非反相超级缓冲器。要了解电路,请注意中心电阻和晶体管构成了一个反相器。反相器输出连接到上部晶体管,同相输入连接到下部晶体管。然后,如果输入为1,则下部晶体管导通;如果输入为0,则借助反相器,上部晶体管导通。然后,如果输入为1,则较低的晶体管将上拉输出,而相应的输出将拉低。如果输入为0,则较高的晶体管将下拉输出,并且对应的输出-起来

N-MOS反相器的问题在于上拉电阻的电流有限。当输出为0时,反相器中的晶体管会以相对较高的电流快速拉低输出。但是,如果输出为1,则输出会被弱得多的上拉电阻上拉。

超级缓冲器类似于CMOS反相器,因为它具有上拉晶体管和下拉晶体管。区别在于CMOS使用P-MOS和N-MOS晶体管,而P-MOS使用反向栅极输入。相反,N-MOS超级缓冲器需要单独的反相器。换句话说,CMOS反相器使用两个晶体管,而超级缓冲器的效率要低得多,因为它需要四个晶体管。

超级缓冲区使用增强模式晶体管上拉和增强模式晶体管下拉。具有自己通道的晶体管的阈值电压低于零,这使其输出可上拉至5 V,并且在较低电压下不会关断。当输出为低电平时,自沟道晶体管将保持导通状态,并且在常规逆变器中的作用类似于正常上拉,因此一定电流将流过该晶体管。您可以在此处阅读有关超级缓冲区的更多信息。

命令寄存器

像大多数处理器一样,8086具有一个指令寄存器,用于存储当前执行的指令。在8086中,命令寄存器保存命令的第一个字节(可以是多个字节),因此它由八个锁存器组成。有人会认为它们是相同的,但是它们每个都有自己的形状。 8086的布局经过高度优化,因此,由于周围导体的局限性,每个闩锁的形状均设计为可充分利用可用空间。特别要注意,一些闩锁连接在一起并共享电源和地。显然,出于相同的原因,闩锁不会连续走动。

所有8个闩锁的形状略有不同,均针对周围的导体进行了优化。在本文的前面,闩锁1旋转了180°。红色垂直线是去除的金属层的痕迹。

车队沿曲折的道路行驶8086。处理器使用性能增强的预取功能,在需要之前从内存中加载指令。它们存储在命令队列中,命令队列是位于一组寄存器中间的6字节队列。相比之下,现代处理器的命令缓存可能高达几兆字节。

执行命令时,它存储在命令寄存器中,大约在芯片的中心。相对较大的距离说明了对超级缓冲区的需求。命令寄存器将命令提供给“组解密ROM”。此ROM定义了命令的高级特性-它是单字节或多字节,或者是命令前缀。这只是复杂的8086指令处理系统的一小部分,其他锁存器存储指令的一部分,标记寄存器的使用和ALU操作,以及由单独的电路控制微码引擎-我将对此进行单独描述。

标记了Crystal 8086,用于命令处理的关键组件。沿着外围,焊线将晶体连接到外部触点。

结论

8086广泛使用动态锁存器来存储内部状态。它们在显微镜下可见,并且其电路可以追踪和理解。8086晶体的分析很有趣,因为与现代处理器不同,它的晶体管大到足以在显微镜下看到。它当时是一个复杂的处理器,带有29,000个晶体管,但足够简单,可以跟踪和理解其电路。