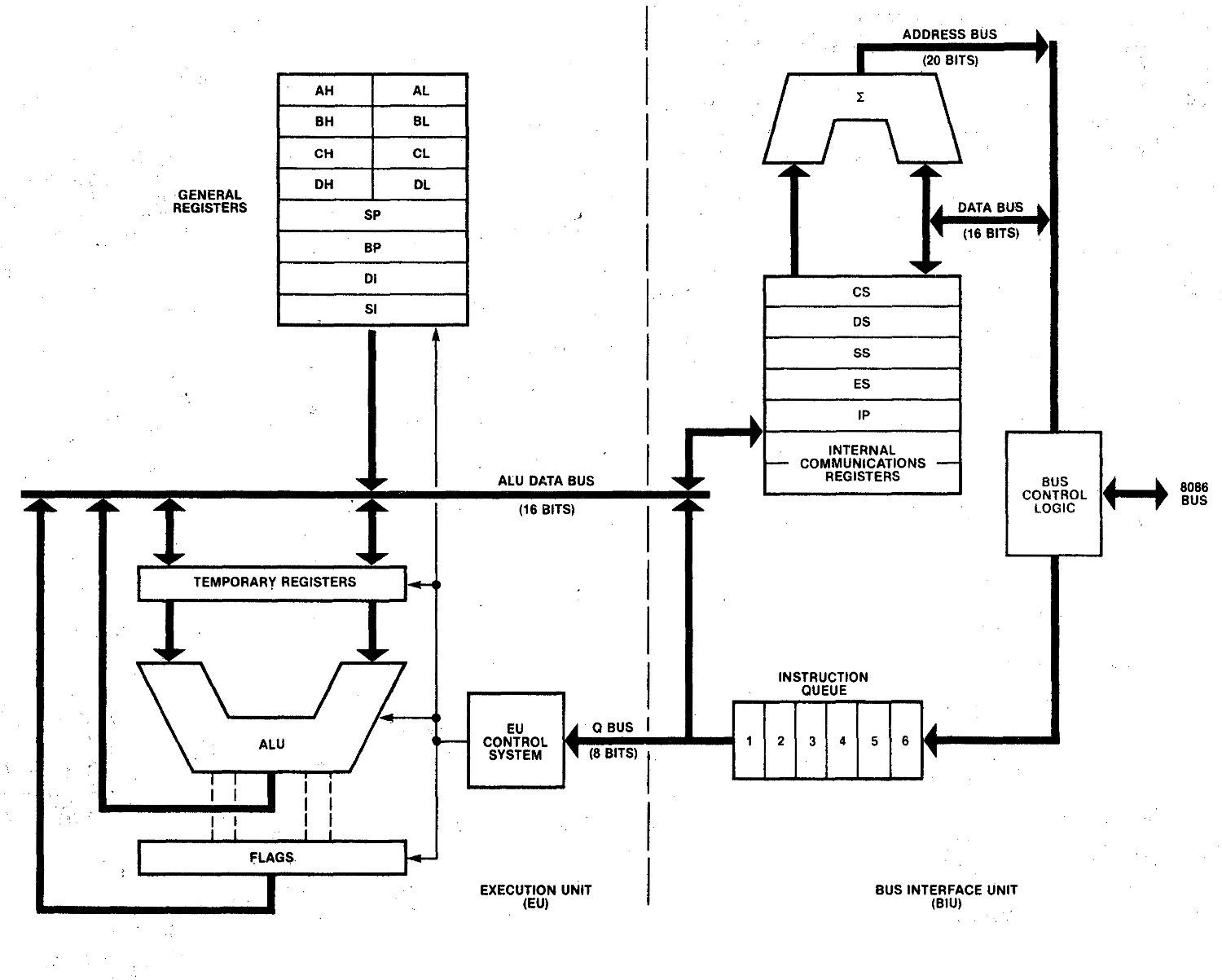

晶体8086。标记了寄存器的存储位置。总线接口模块将高位寄存器用于存储器访问,而执行模块将低位通用寄存器用于存储器访问。命令缓冲区是一个6字节的预请求命令队列。

该照片显示了显微镜下的8086处理器的图像。在芯片顶部可以看到一个金属层,在该金属层下隐藏着硅。位于连接线的外边缘,将芯片上的焊盘连接到芯片的40个外部引脚。

15个16位8086寄存器和6个字节的命令预请求队列(代码预取)被框架化。寄存器占据了晶体的很大一部分,尽管总的说来,它们只能输入36个字节。由于空间限制,早期的微处理器具有相对较少的寄存器。相比之下,现代处理器芯片具有千字节的寄存器和兆字节的缓存。

8086是最早实现代码预取的微处理器之一,但是Motorola 68000(1979)早些时候具有4字节的预取缓冲区。在大型机中,可以使用IBM Stretch(1961),CDC 6600(1964)和IBM System / 360 Model 91(1966)进行预取。现代处理器中

的寄存器数量很难计算。我发现的唯一确切数字是《高速微处理器的解剖学》一书“(1997年)详细描述了AMD K6处理器。由于寄存器的重命名,现代处理器的物理寄存器要比体系结构的寄存器(程序员可以看到的物理寄存器)多得多,并且文档中未指出物理寄存器的数量。K8除外,只有八个x86寄存器。一般情况下,有16个微体系结构工作寄存器需要重

命名。支持AVX-512的处理器具有32个512位寄存器,即为此功能保留了2 KB寄存器。在这种情况下,寄存器的大小甚至更难以计算。然后在高级处理器中,其容量达到77 MB。

如何在芯片中实现寄存器

我将从描述8086如何由N-MOS晶体管构建开始。然后,我将解释如何制作反相器,如何将单个位存储在反相器中以及如何制作寄存器。

与那个时代的其他芯片一样,8086也基于N-MOS晶体管。这些芯片由硅衬底组成,砷或硼杂质扩散到硅衬底中以形成晶体管。在硅上方,多晶硅导体形成晶体管的栅极,并将所有组件相互连接。位于更高位置的金属层包含额外的导体。相比之下,现代处理器使用CMOS技术,该技术结合了N-MOS和P-MOS晶体管,并包含许多金属层。

下图显示了一个逆变器由N-MOS晶体管和电阻组成。当输入电压低时,晶体管关闭,因此上拉电阻将输出上拉。当输入电压高时,晶体管导通,将地与输出相连,将输出拉低。因此,输入信号被反相。

实际上,N-MOS阀中的上拉电阻是一种特殊的晶体管。甲耗尽晶体管表现得像一个电阻同时更加紧凑和有效。

该图显示了如何由晶体管和电阻器制成反相器。图为芯片上的实现。金属层已被去除以显示硅和多晶硅。

上图显示了8086逆变器的物理制造方式,粉红色区域是带有杂质的硅,使其具有导电性,铜色线的顶部是多晶硅。晶体管出现在多晶硅与硅相交的地方。多晶硅形成晶体管的栅极,两侧的硅部分提供源极和漏极。一个大的多晶硅矩形在+5 V和输出之间形成一个上拉电阻。因此,芯片的电路与逆变器的电路相同。这样的电路可以在显微镜下观察和反向工程。

寄存器的构造块是反馈环路中的两个反相器,存储一位(见下文)。如果顶部导体为0,则右变频器将向底部导体输出1。然后,左逆变器将向顶部导体输出0,从而完成循环。因此,电路是稳定的并且“记住”0。反之亦然,如果上部导体为1,则它将在下部导体上变为0,而在上部导体上变为1。结果,该链可以存储0或1,从而形成一个一位的存储器。

8086具有两个成对的反相器,它们将一位存储在一个寄存器中。电路稳定地处于状态0或1。

将三个晶体管添加到该对反相器以创建可用的寄存器单元。一个晶体管选择一个单元进行读取,第二个晶体管选择一个单元进行写入,第三个晶体管在读取时放大信号。在下面电路的中心,两个反相器存储该位。为了读取该位,将电流施加到红色总线。这将反相器的输出通过放大晶体管连接到位线。为了写入位,电流施加到红线,红线将位线连接到反相器。通过将0或1的高电流信号施加到位线(以及相应地施加到存储的位),我们迫使逆变器切换到所需值。注意,位线用于读取和写入。

其他处理器使用的寄存器位置略有不同。当写入新值时,6502在逆变器反馈环路中使用附加晶体管断开电路。 Z80同时写入两个反相器,这“使更改变得容易”,但是需要两根线才能写入。 8086在每个寄存器位置都有一个增益晶体管,用于读取,而其他处理器则读取两个反相器的输出,并使用外部差分放大器放大信号。寄存器8086的基本单元由7个晶体管(7T)组成,这比使用6个或4个晶体管的典型静态RAM单元要多,但它仅使用一条位线,而不使用两个不同的位线。动态内存(DRAM)效率更高,并使用单个晶体管和电容器,但是,如果不更新数据,它将丢失。

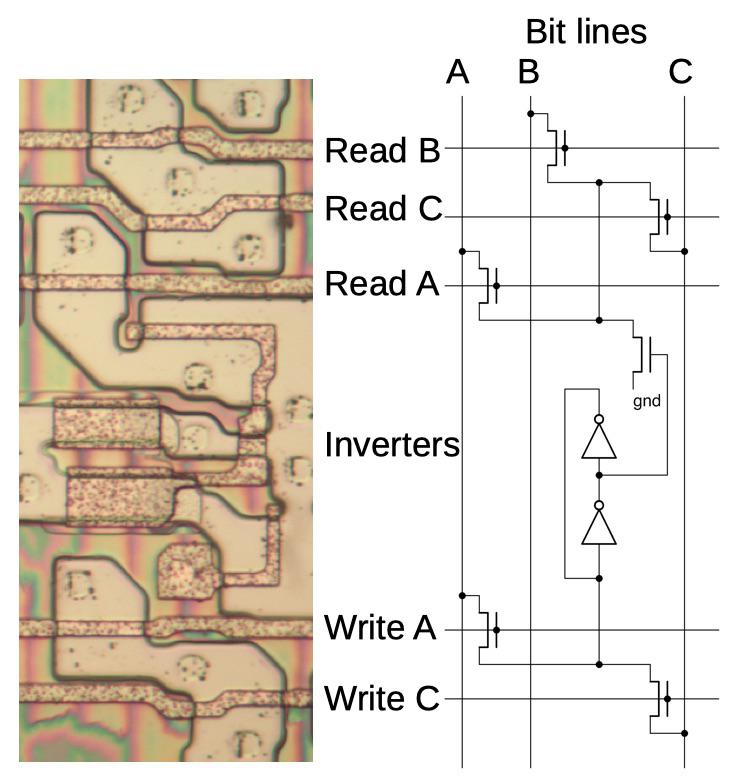

存储位的寄存器单元的示意图。寄存器文件由此类单元格的数组组成。

寄存器文件由类似于上述寄存器单元的矩阵组成。由于寄存器存储16位值,因此矩阵的宽度为16个单元。每个寄存器都水平放置,因此读或写总线会选择特定寄存器的所有单元。 16条垂直位线形成一条总线,因此所选寄存器中的所有16位都是并行读写的。

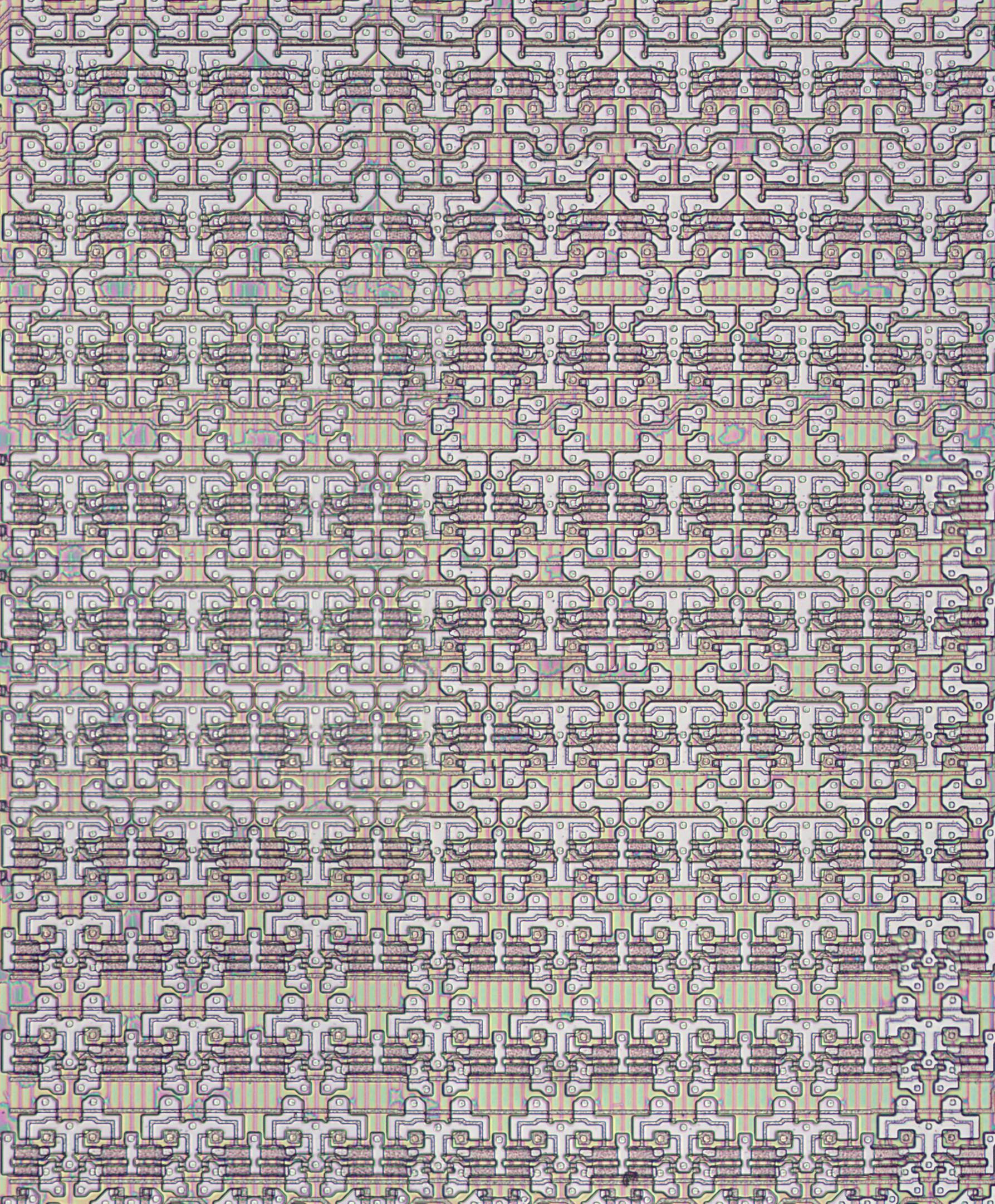

下图显示了一个放大的通用寄存器文件8086,其中显示了寄存器单元矩阵:16列8行,8个16位寄存器。然后给出文件中一个寄存器位置的增量。让我解释一下如何实现此单元。

8086 ( 16- ), . , .

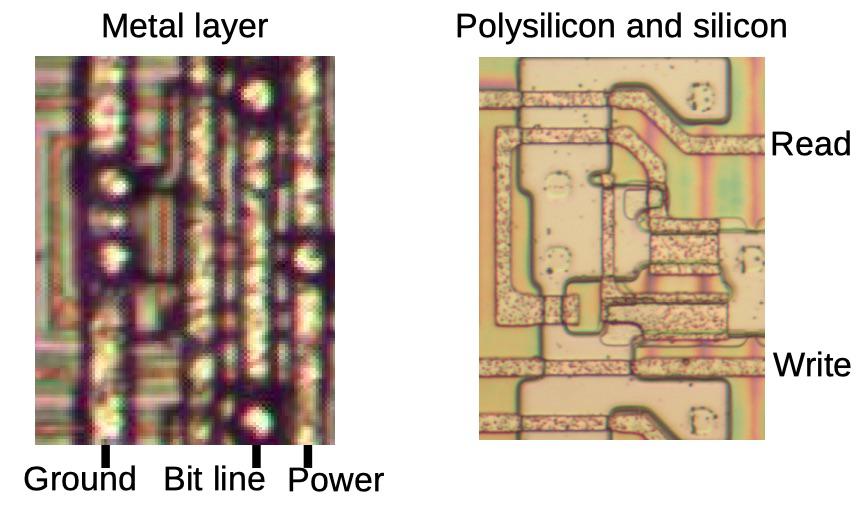

8086由掺杂的硅和多晶硅导体制成,顶部带有金属导体。下面的左图显示了寄存器单元的垂直金属导体。标记了地线,电源线和位总线线(其余线穿过寄存器文件,但未与其接触)。在右侧的照片中,金属层已溶解,因此可以看到多晶硅和硅。读取和写入总线是水平多晶硅导体。由于芯片只有一层金属层,因此在垂直总线的寄存器中使用金属,在水平总线的寄存器中使用多晶硅,这样它们就不会相互交叉。通过接头的金属和硅在金属照片中显示为明亮的圆圈,在硅照片中显示为圆圈。

注册存储位置。左图为金属层,右图为多晶硅和硅的对应层。

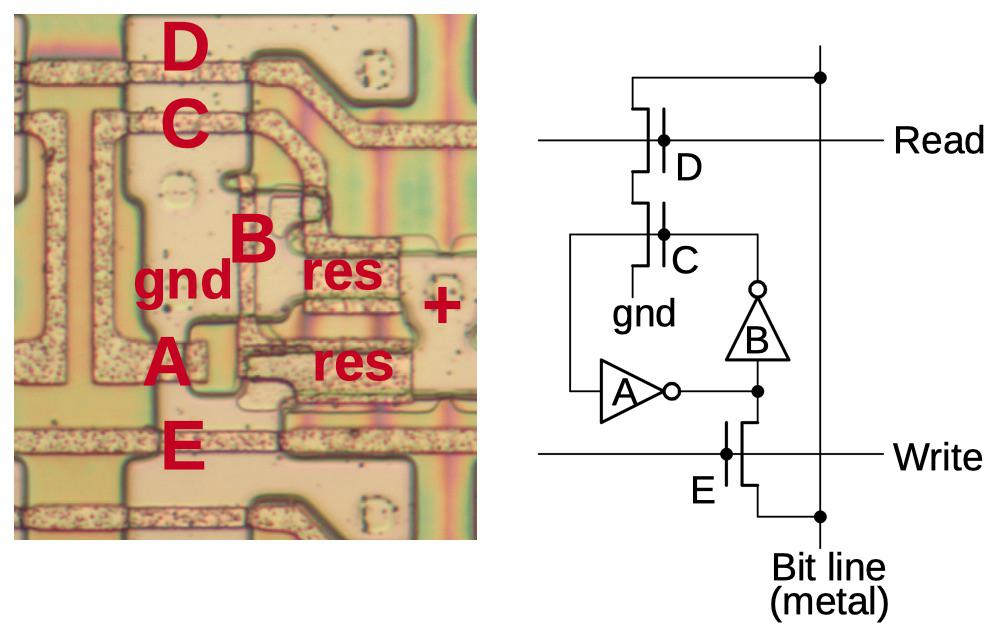

下图显示了寄存器单元的物理方案与主体方案的对应关系。反相器由晶体管A和B以及寄存器组成。晶体管C,D和E由标记的多晶硅片形成。位线不可见,因为它位于金属层中。注意,存储器单元的布局已进行了优化,以最大程度地减小尺寸。还要注意,晶体管A比其他晶体管小得多。反相器A具有相当低的输出电流,因此写入时位线可以克服它。

用相应的电路对8086中的单元进行寄存器

8位寄存器支持

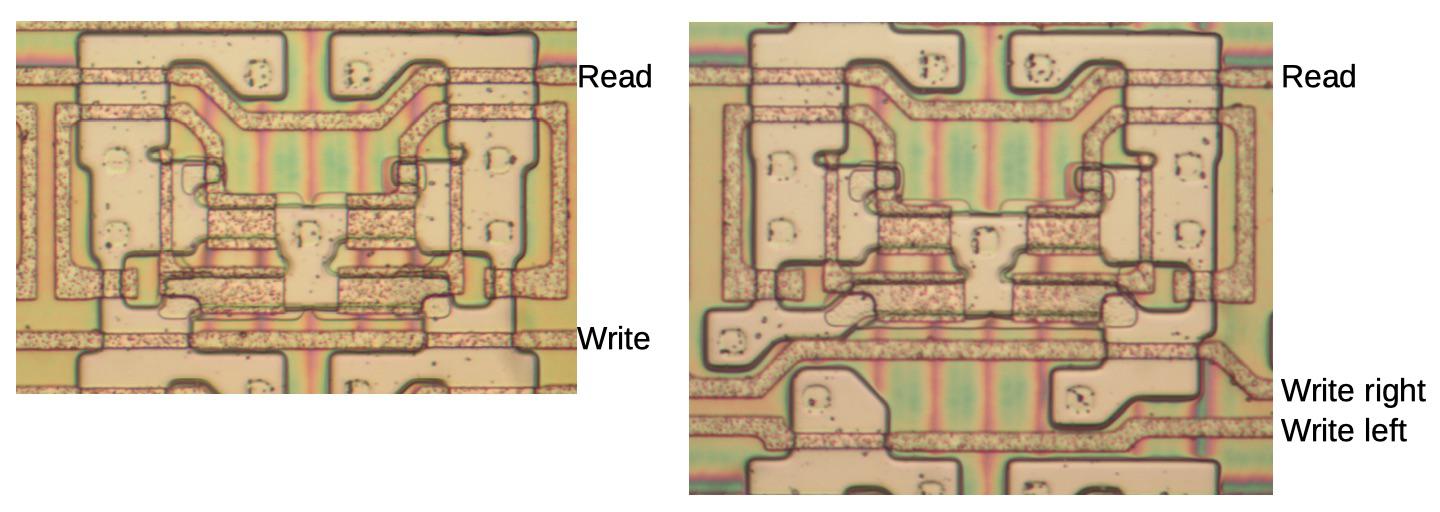

如果仔细检查晶体,您会发现某些寄存器单元的结构略有不同。左边是我们已经讨论过的寄存器位置,右边是一对带有两个写总线(而不是一个)的寄存器位置。在左图中,写总线穿过两个寄存器单元中的硅。在右图中,“右写”总线穿过右侧的硅,但在左侧的硅之间运行。相反,“左写”线穿过左侧的硅并在右侧的硅区域之间延伸。因此,一个总线控制右位的写入,而另一根总线控制左位的写入。在16位寄存器中,可以用这种方式分别写入8位交错部分。

晶体上的寄存器单元不会均匀重复-每隔第二个单元都是前一个的镜像。这增加了寄存器单元的密度-在两个镜像单元之间运行的电源轨可以为它们两者供电(接地也是如此)。镜像重复可以将所需的电源和接地轨数量减少一半。

尽管框图通常显示了如何将16位寄存器分为左右两半,但在现实世界中,每一侧的位都是交替的,而不是总是将第一个8位部分存储在左侧,第二个部分存储在右侧。这种实现方式简化了有时出现的将16位字的两半交换的任务。一种这样的情况是不对齐地读取或写入存储器。另一个是使用寄存器的上半部分(例如AH)的ALU操作。在左右两半之间交换位将需要在字半的所有位之间拉长线。然而,在交替布置中,为了交换一个单词的两个半部,有必要交换每对相邻的位,这不需要长线。换一种说法,8086的交错寄存器使对导体进行布局变得容易,以将一个单词的两半互换。

两对具有不同电路的存储单元。左侧的单元具有一个写总线,而右侧的单元则具有分别用于左位和右位的写总线。

为什么有些寄存器有两个写总线,而另一些却有一个?原因是8086具有16位寄存器,但是其中的四个可以按8位访问,如下所示。例如,可以将16位累加器A作为8位AH(累加器的高位)和8位AL(低端)寄存器来访问。用两个写控制总线实现寄存器允许分别写入寄存器的每一半。

如果寄存器文件仅支持16位寄存器而不是8位寄存器,则处理器可能会工作,但效率较低。通过读取全部16位,更改8位一半并写入全部16位来完成对8位一半的写入。结果,调用将转到三个寄存器,而不是访问一个寄存器。在这种情况下,寄存器文件不需要以某种方式特别支持读取8位,因为不必要的一半可以简单地忽略。

8086中的通用寄存器。寄存器A,B,C和D可分为两个8位半部分。

多端口寄存器

到目前为止,我们已经介绍了八个通用的“下层寄存器”。 8086还具有七个用于内存访问的“上层寄存器”,其中包括臭名昭著的段寄存器。这些寄存器具有更复杂的多端口操作方案,允许同时执行多个读取和写入过程。例如,通过多端口寄存器文件,您可以同时读取程序计数器,段寄存器和写入另一个段寄存器。

下面的框图与大多数框图不同。对于8086,因为它显示了处理器的真实物理实现,而不是程序员所想象的。特别是,该图显示了总线接口模块的寄存器中的两个“内部通信寄存器”(右),以及与芯片上可见的7个寄存器匹配的段寄存器。下面显示的临时寄存器实际上是ALU的一部分,因此我将不在本文中介绍。

《设计现代处理器》一书讨论了2000年代以来处理器中的复杂寄存器系统。它说电路复杂度很快超过了三个端口,并且某些高级处理器的寄存器文件具有20个或更多端口。

下面的多端口寄存器单元基于相同的两个反相器电路,但是它具有三条位线(与前一种情况不同)和五条控制线(而不是两根)。三个读取总线允许您读取三个位线上的任何一条寄存器单元的内容,而两个写入总线则允许位A或C写入寄存器单元。

8086处理器中的多端口寄存器单元

乍一看,8086寄存器文件看起来像是一组同类的寄存器,但仔细观察可知,每个寄存器都根据其功能进行了优化。其中一些是简单的16位寄存器,并且位置最紧凑。其他16位寄存器可以作为两个8位寄存器访问,这需要另一个控制总线。最复杂的寄存器有两个到三个用于读取的端口,一个或两个用于写入的端口。在每种情况下,寄存器单元的物理实现都经过精心设计,以占用尽可能少的空间,因此,晶体管的形状通常很复杂。英特尔工程师尽可能严格地压缩寄存器的布局,以使其全部适合其可用空间。

高位寄存器具有不同数量的端口用于读写:两个寄存器具有3条读取和2条写入总线,一个寄存器具有2条读取和2条写入总线,四个寄存器具有2条读取和1条写入总线。前三个寄存器可能是程序计数器,间接临时寄存器和临时操作数寄存器。后四个可能是SS,DS,SS和ES段寄存器。还有三个指令预取缓冲寄存器,每个寄存器具有一个读总线和一个写总线。

最初的IBM PC中使用的8088处理器实际上与8086相同,不同之处在于它具有8位外部总线而不是16位总线,因此系统便宜。 8088的预取缓冲区是4个字节而不是6个字节-可能是因为4个字节足以应付8088较慢的内存总线。

与8086不同,8088的预取寄存器支持对8位半部分的独立写入(类似于8088的A,B,C和D寄存器,只有这些单元看起来不同)。这是因为由于总线较窄,8088一次请求一个字节,而不是一次一个字。因此,预取寄存器必须支持字节写,而8086支持字预取。

高位寄存器文件,由十个16位寄存器组成。图为硅和多晶硅。垂直红线-去除的金属层的残留物。可点击的。

结论

尽管8086处理器已经使用了42年,但它仍然对现代计算机产生重大影响,因为x86体系结构在今天仍然非常常用。寄存器8086在现代x86计算机中仍然存在,尽管今天它们已经是64位长了,除了这些寄存器之外,还有许多其他寄存器。

8086晶体的研究非常有趣,因为可以在显微镜下观察其晶体管。曾经它是一台复杂的处理器,因为它装有29,000个晶体管,但是足够简单以跟踪所有电路并了解它们的工作原理。

也可以看看: