您是否想知道如何获得设计飞船电子设备的工作?我最近收到了一份邀请函,以采访Blue Origin的FPGA设计师的职位(见上文)。就我个人而言,我不需要这样的职位(我已经在另一家公司中担任过ASIC设计师的职位),但是我注意到,Blue Origin申请人的技术要求与将于9月15日至17日举行的针对中小学生的研讨会的内容完全一致。在RUSNANO的支持下,在Skolkovo的ChipEXPO展览会上。当然,尽管在研讨会上,我们将仅在最开始的级别上接触Verilog和FPGA技术:基本概念和简单但已经很有趣的示例。要在Blue Origin获得这份工作,您还需要几年的学习和工作。

由于冠状病毒,该研讨会将是遥远的,因此不仅莫斯科的学童和学生,而且俄罗斯,乌克兰,哈萨克斯坦,加利福尼亚和其他国家和地区的所有人都将能够参加。 MIET,HSE MIEM,MIPT,切尔尼戈夫理工大学,萨马拉大学,IVA Technologies和fpga-systems.ru的讲师和工程师将亲自进行讲座并为参加者提供远程帮助。

要首先参加,甚至在研讨会之前,您都需要完成RUSNANO的理论课程的三个部分,其总标题为“智能纳米芯片的创造者如何工作”:“从晶体管到微电路”,“数字电路的逻辑端”,“数字电路的物理端”。这门课程是必不可少的,以便您了解研讨会期间的工作。收到理论在线课程的结业证书后,您可以前往RUSNANO在莫斯科的办公室,并获得免费的实践研讨会费用(如果他们留下来,则优先考虑学童)。使用此面板,您可以在Skolkovo研讨会之前,之中和之后在家中工作。

如何获得报酬,为研讨会做准备以及它将进行哪些工作:

您可以在STEMford网站上找到有关如何收取费用的说明。 STEMford是来自RUSNANO基础设施教育计划基金会的子公司eNano的中小学生教育计划。在这里可以访问他们的办公室:

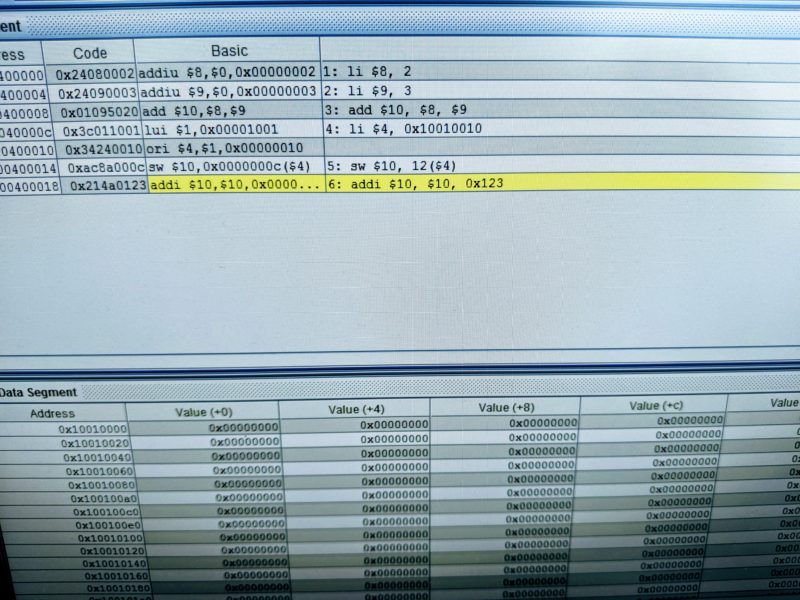

在进行实验之前,您需要在计算机上安装Intel Quartus Prime Lite Edition。有关如何执行此操作的说明,请参见A. Yu。Romanov,Y。V. Panchul编辑的“数字综合:实践课程”一书的免费片段。 DMK Press,2020

年。总体而言,“数字综合”是一本对研讨会有用的书,它描述了将在研讨会上作一些改动的练习,尽管例如,它代替了更现代的schoolMIPS教育处理器。schoolRISCV: 在《数字综合》一书的最后,有一对新婚夫妇弗拉迪斯拉夫(Vladislav)和埃琳娜·莎尔辛(Elena Sharshin)的访谈颇为有趣,英特尔与他们的同事安德烈·帕普申(Andrei Papushin)一起将英特尔带到了加利福尼亚,以在InnovateFPGA竞赛中获得银牌 。如果没有足够的主板你,或者如果你是不是学生,你可以在全球速卖通,并在其他地方订购板:1,2,3,4: 将发生在本次研讨会是什么?这是程序的一部分:

15 . .

: , « » ().

15.00. , .

15.15-15.30. -: Apple iPhone: .

, . , .

15.30-16.00. : Verilog. /FPGA Intel Quartus Prime Lite Edition. .

16.00-16.30.

///-, , c .

16.30-17.00. .

17.00-17.30. : , .

17.30-18.00. .

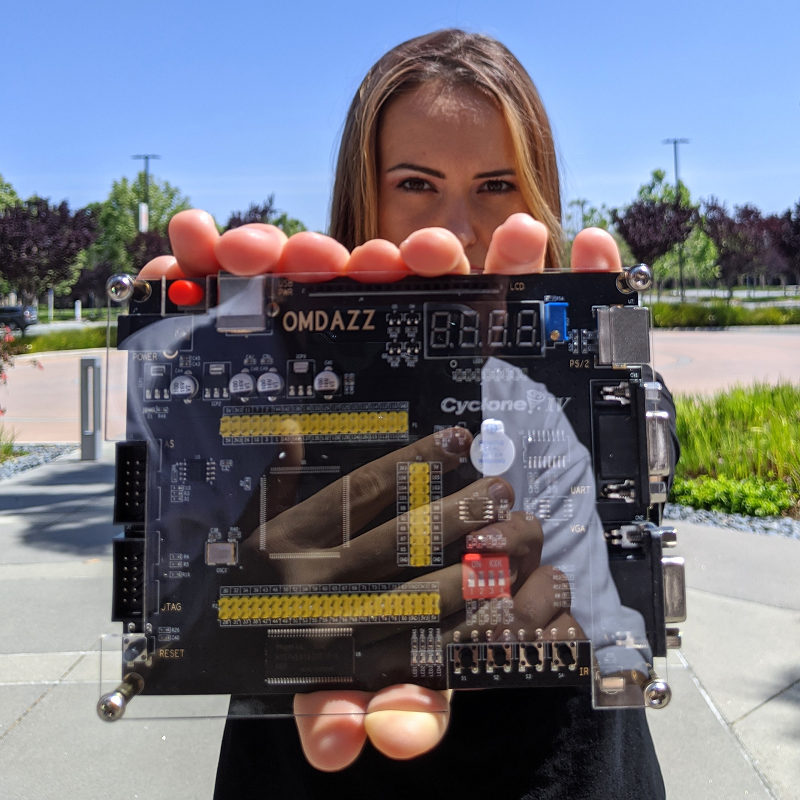

18.00-19.00. ZEOWAA OMDAZZ Intel FPGA Cyclone IV: : ( ). Terasic DE10-Lite Intel FPGA MAX10: : ( ).

19.00-21.00. , : , , ,

.

第一天是基于去年在莫斯科举办的研讨会的经验,这在一篇有关哈布雷的文章中进行了描述:

第二天是基于去年在Zelenograd举办暑期学校和在萨马拉举办的研讨会的经验:

16 . .

: , , , .

15.00-15.15. -: : , .

.

15.15-15.30. : VGA.

.

15.30-16.00. .

16.00-16.30. . Digilent Basys3 Xilinx FPGA Artix-7. .

, fpga-systems.ru.

16.30-17.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

17.00-17.30. : Linear Feedback Shift Registers (LFSR) . Verilog VHDL LFSR . LFSR VGA .

, .

17.30-18.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

18.00-19.00. .

.

18.00-21.00. , . .

第三天将基于Stanislav Zhelnio和Alexander Romanov的处理器培训课程的经验。在他们开发和使用schoolMIPS学习处理器之前,现在我们将使用schoolRISCV。 RISC-V架构与MIPS和其他RISC架构(SPARC,ARM,POWER等)非常相似,但清除了拐杖,这在简单的处理器上是有意义的,但是会干扰复杂的处理器(SPARC中的注册窗口,在软件中没有意义)一个大堆栈; MIPS中的Rev6之前的分支延迟槽,这在具有顺序读取指令的简单静态流水线上很好,但是在动态流水线中却让人头疼。

由于在俄罗斯,至少有三家公司在RISC-V架构上设计处理器,并且这对于将来的高端俄罗斯嵌入式甚至台式机和服务器处理器都是不错的选择,并且因为RISC-V可以自信地取代MIPS来工作世界大学的建筑和微建筑实验用马匹,那么小学生最好在上面教书。

17 . .

— , ..., . .. (), « » ( ).

15.00-15.15. -: ENIAC , IBM/360 Cray-1 Intel, ARM RISC-V: , .

.

15.15-16.30. : . RISC-V .

, - .

16.30-17.30. : . schoolRISCV, . .

, IVA Technologies.

17.30-17.30. . .

.

17.30-18.00。结束语:掌握数字电路设计并将其应用于嵌入式系统设计和人工智能计算加速器的下一步。

亚历山大·尤里耶维奇·罗曼诺夫(Alexander Yurievich Romanov)。

18.00-21.00。其他练习和个别项目,供学生更换处理器并将其与外围设备集成。在参与大学的微电子学的本科生和研究生的帮助下。

去年夏天,这是斯坦尼斯拉夫·兹列尼奥(Stanislav Zhelnio)在泽列诺格勒(Zelenograd)教小学生

的故事:在斯科尔科沃(Skolkovo)的虚拟ChipEXPO研讨会上见!我们将尝试在MIET,HSE MIEM和MIPT的老师的帮助下在现场举行活动的一部分,并进行现场直播,但是如果病毒不允许,我们将以分布式方式进行。