值得注意的是,MOS结构仍在工作,但已大大减少,而大多数事情不能仅仅这样减少。例如,您不能将电动机缩放10倍并期望它能工作。大多数物理对象都受方立方定律的困扰:对象的面积像线性正方形一样增长,其体积像立方体一样增长。但是,在MOS结构的情况下,缩放时的大多数组件要么保持不变,要么提高(例如,频率和功耗)。有关扩展的更多详细信息,请参见Mead和Conway的《VLSI系统简介》。...具有讽刺意味的是,1978年的书声称缩放由于物质的物理特性而对通道长度具有基本的四分之一微米(250 nm)限制。事实证明,这种限制存在着难以置信的缺陷-由于FinFET之类的技术,现在晶体管正朝着5 nm的特征尺寸发展。

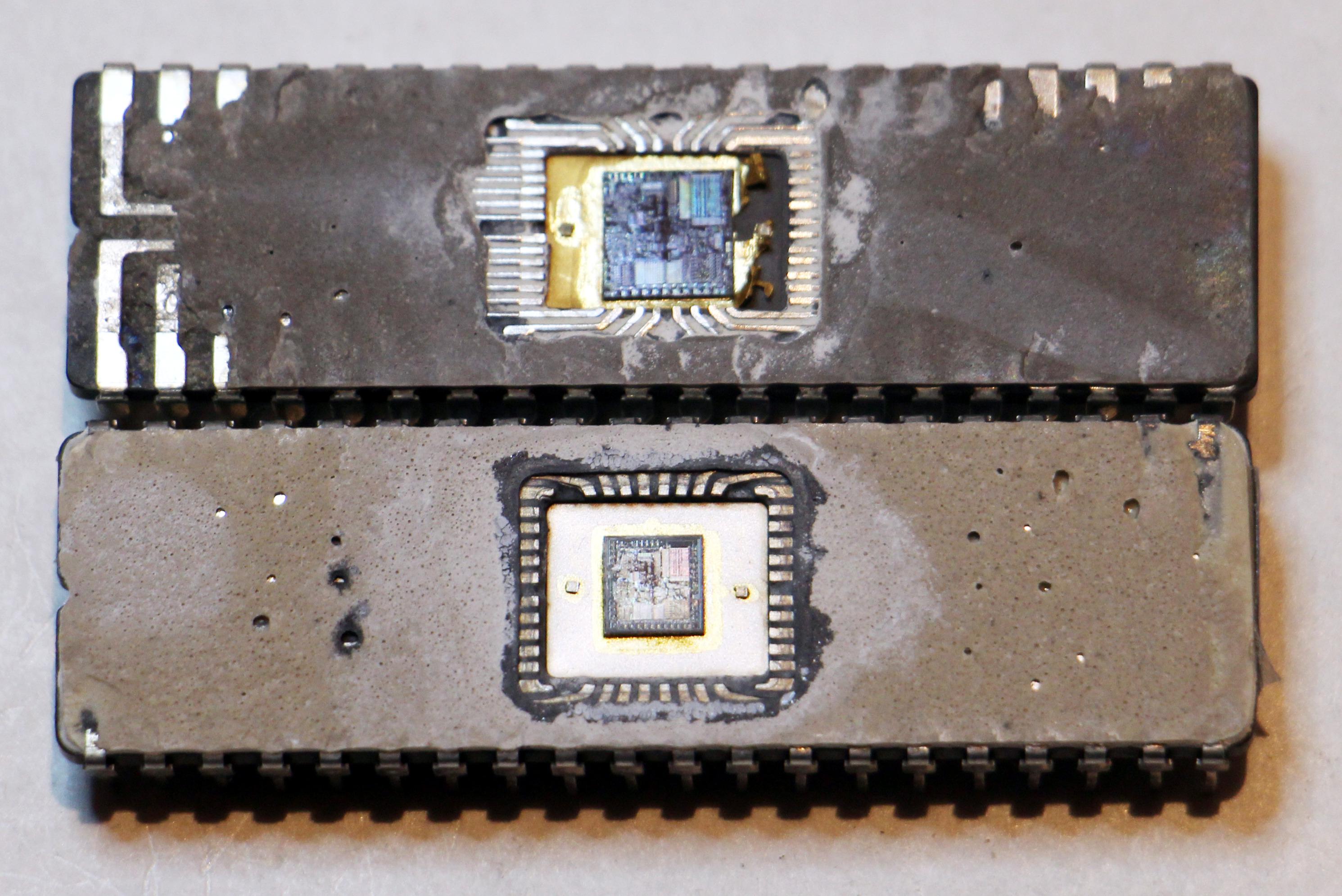

下图显示了1979年的8086芯片,以及其1986年明显更小的管芯版本。陶瓷盖已经从芯片上移开,以便可以看到晶体。在更新的8086中,内部电路的长度比原始电路减少了64%,因此占原始面积的40%。晶体本身并没有被大量还原。它占原始面积的54%。处理器外壳没有改变,DIP 40针虽然经常用于微处理器。

老芯片的表壳上写着'78,'79,而表盘上则是1979,底部的日期代码是7947(1979年第47周)。 1978年写在新芯片的表壳上,1986年写在水晶上,没有日期代码。因此,应在1986年或更晚些时候制造。目前尚不清楚为什么表壳上的新芯片日期更早。

比较两个8086芯片,新芯片的底部芯片小得多。右上方的矩形是微代码ROM。

8086是有史以来最具影响力的芯片之一。它标志着仍然主导台式机和服务器计算机的x86体系结构的开始。与现代CMOS处理器不同,8086建立在N-MOS晶体管(如6502,Z-80和其他早期处理器)上。第一个芯片是使用HMOS技术制造的,正如英特尔所说的那样。在79年,英特尔推出了它的高级版本HMOS-II,在82年,它切换到了HMOS-III,该过程用于制造我的两款芯片的较新版本。 HMOS的每个后续版本都会缩小芯片组件的尺寸并提高效率。

N沟道MOSFET是MOSFET的特定类型。它们的效率比早期微处理器(例如Intel 4004)中使用的P沟道MOS结构要好得多。现代处理器一起使用N沟道和P沟道晶体管来降低功耗-这就是所谓的CMOS。...由N沟道MOSFET制成的栅极需要一个上拉电阻,该电阻是一个晶体管。耗尽型负载晶体管是1970年代中期推出的一种晶体管。这种类型的晶体管更适合用作上拉电阻,并且不需要额外的电源电压。最后,MOSFET最初使用金属来创建栅极(MOSFET中的字母M)。但是,在1960年代后期,飞兆半导体开发了多晶硅来代替金属。结果,芯片更有效并且更容易制造。结果,从1960年代末到1970年代中期,MOS结构的生产发生了一些根本性的变化,从而导致了6502,Z-80、8085、8086和其他早期处理器的成功。在1980年代,CMOS处理器取代了它们,因为它们速度更快,功耗更低。

奇怪的是,首字母缩写词HMOS中的H到底代表什么并不完全清楚。我还没有找到来自英特尔的这个缩写的笔录。该规范称“英特尔先进的硅N沟道HMOS栅极制造工艺”或“ HMOS是一种高效的n沟道MOS工艺”。英特尔后来将CHMOS描述为互补高速金属氧化物半导体[complementary high speed metal oxide semiconductor]。摩托罗拉已将HMOS确定为高密度MOS。其他来源将其描述为具有短沟道的高速MOS或高密度MOS。英特尔拥有专利对于“ MOS工艺和高密度高速器件”,因此H可能代表“高密度”和“高速”。

有趣的是,在使用微处理器和其他芯片的处理程序之前,英特尔使用4K静态RAM来开发每个HMOS处理程序。她使用了RAM芯片,可能是因为它的电路非常密集,但是由于相同的存储单元一遍又一遍地重复,因此它的设计也相对容易。一旦制定了所有电路布局规则,便可以开始构建更加复杂的处理器。

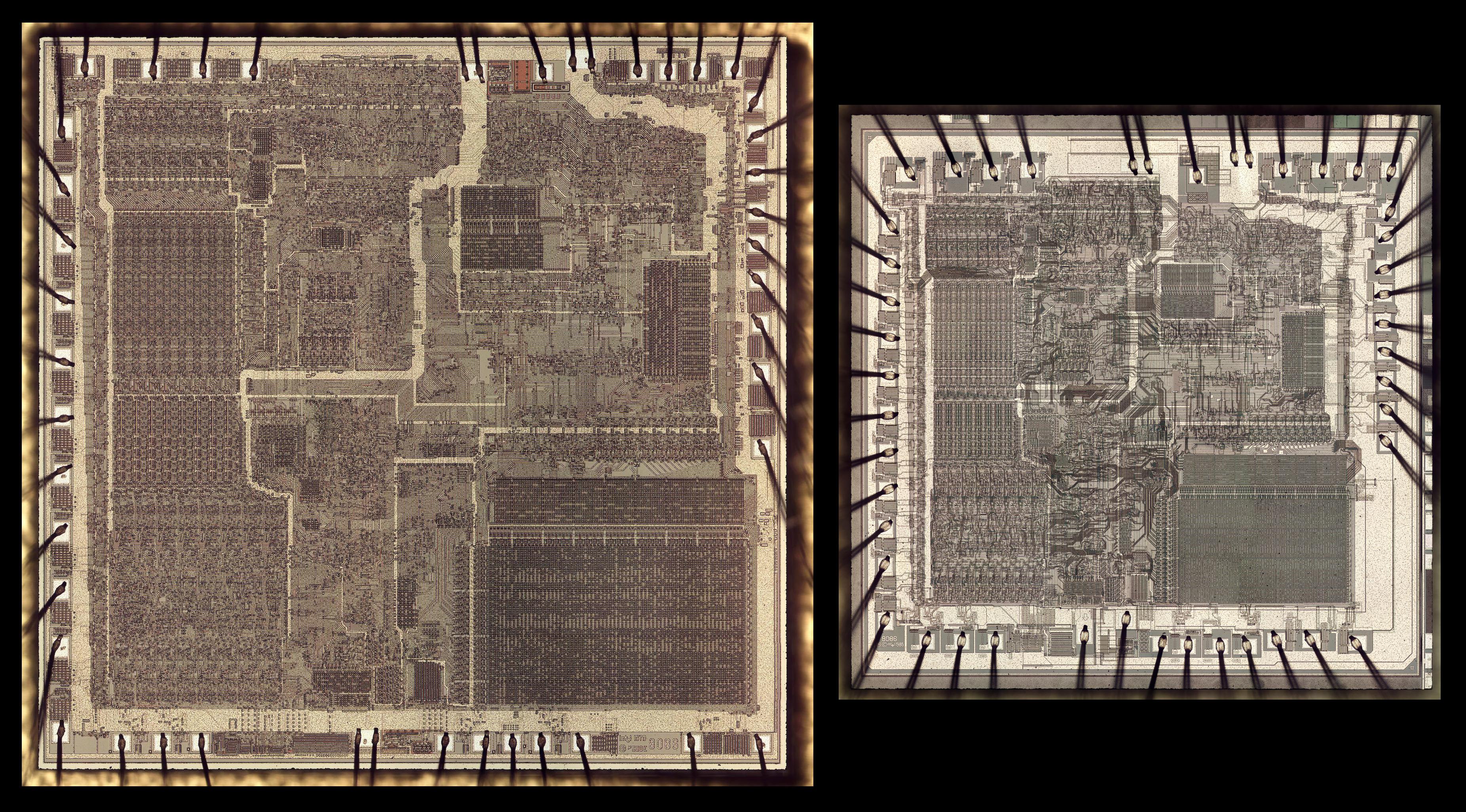

两个版本的8086晶体具有相同的比例。传入导体连接到位于晶体周围的焊盘。

上面的照片以相同的比例显示了两种版本的8086晶体。尽管乍看之下,这两个芯片的内部组件布局相同,但看起来似乎有所不同。中间右侧的芯片上有许多暗线,而左侧左侧的芯片上没有,但这只是一个拍摄假象。这些线是位于金属下方的一层多晶硅。在晶体的左侧,所有导体都以相同的方式放置,只是在照片中它们非常苍白。我认为新芯片的金属层更薄,这就是为什么多晶硅的外观更好的原因。

我按比例缩放了这两种芯片的高分辨率照片,以进行比较,结果发现,这些芯片的主要部分完全相同,除了一些微小的差异。唯一的问题是微码中是否有更改。从外部看,它们看起来相同,但是我没有一点一点地比较它们。

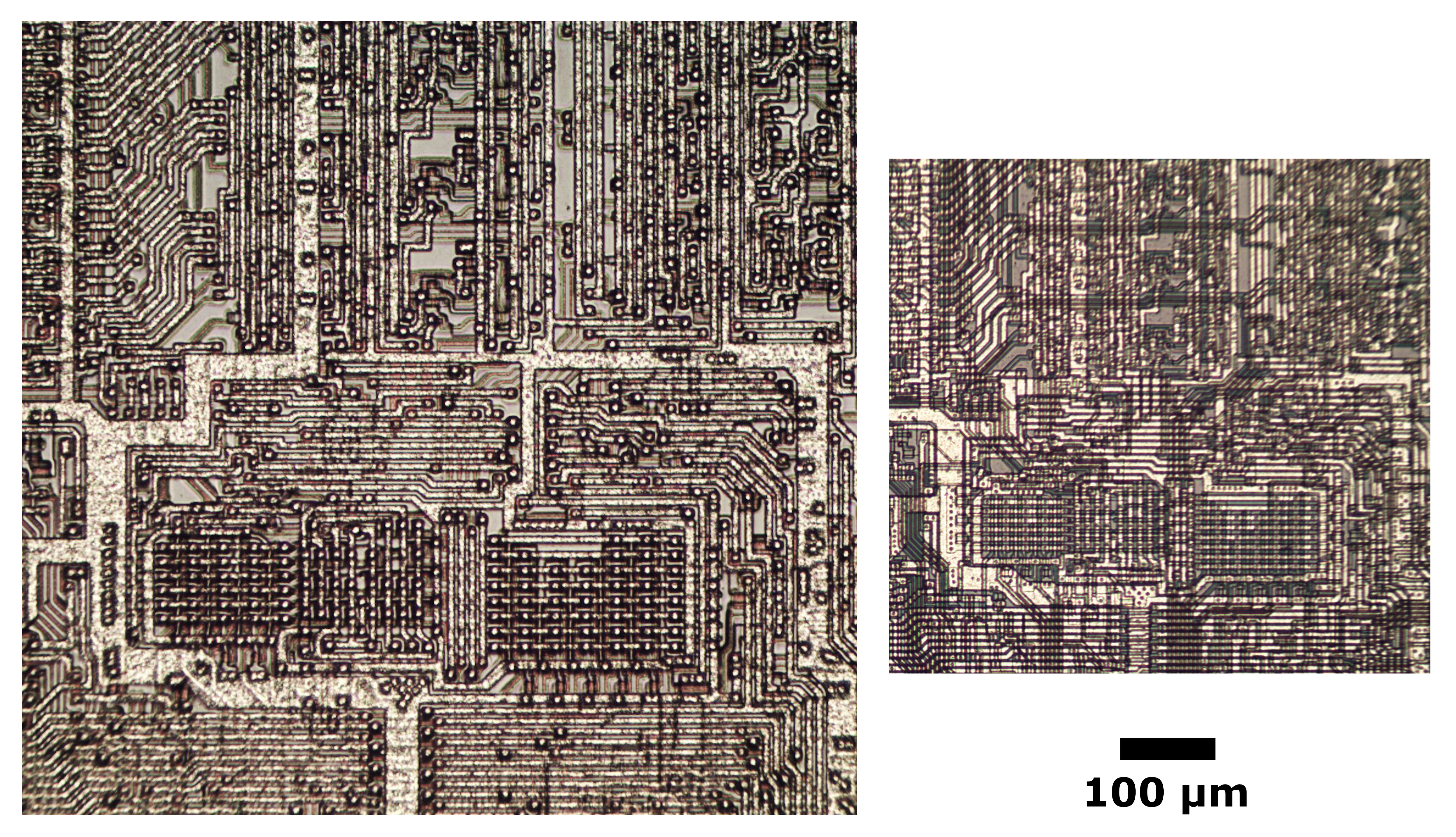

下面的放大照片显示了两个晶体的相同链。您可以看到组件之间的确切对应关系,这证明电路仅在尺寸上减小了,而没有重做。在照片中,金属层位于芯片顶部。右图显示了一些多晶硅。

在两个不同芯片上以相同的比例绘制相同的情节

但是沿着晶体的周边,差异是显着的。接触垫靠得更近,尤其是在右下角。有两个原因。首先,接触垫不能显着减小,因为它们需要用连接线连接。其次,配电线路的边缘变宽以维持所需的电流。例如,查看照片的右下方,微码RAM的右侧。尤其是这样做是因为电路中间的电源走线和其他所有内容都按比例缩小,因此外部走线需要补偿这些损耗。另外,新芯片中较薄的金属层不能支持相同的电流,除非将其扩展。

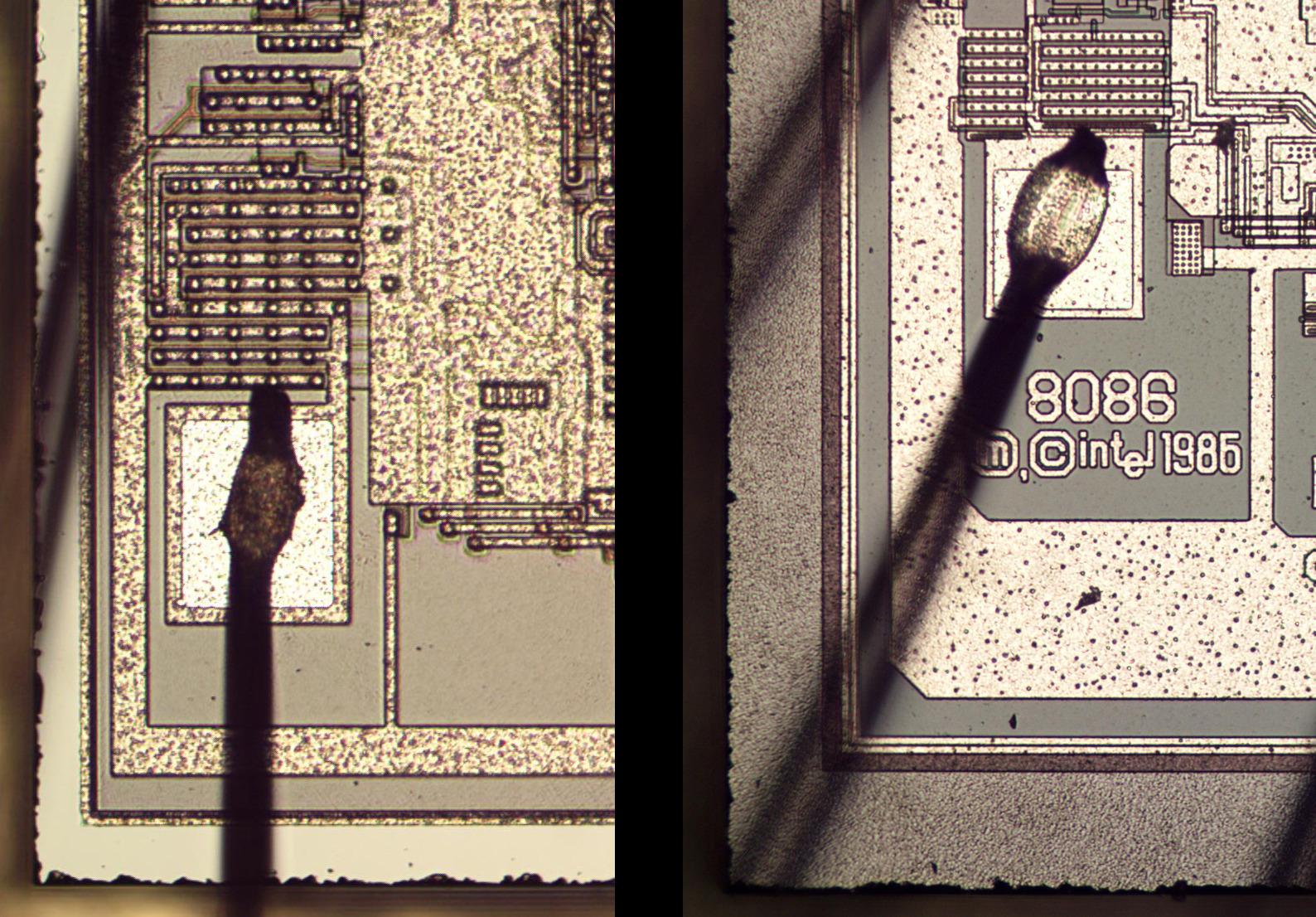

旧芯片(左)和新芯片(右)上的接触垫和随附的晶体管。版权日期中的数字“ 6”具有不寻常的平顶-看起来是将“ 5”更正为“ 6”。

上面的照片显示了带有焊接跳线的焊盘。晶体管位于焊盘上方。新芯片的位置几乎相同,但晶体管尺寸减小并重新设计。请注意,新芯片上的金属导体要厚得多。英特尔徽标从右向左移动,可能是因为有可用空间。

让我们仔细看看晶体

首先,介绍了8086和该时代其他芯片中使用的n沟道MOS的生产历史。这些芯片由硅基板组成,在硅基板上添加了砷或硼杂质以形成晶体管。顶部的多晶硅层为晶体管创建了栅极,并使将元件与导体连接成为可能。最后,顶部的一个金属层将所有组件粘合在一起。

半导体制造工艺(例如,HMOS-III)对于某些最小尺寸和组件(硅,多晶硅和金属层)之间的距离具有某些规则。如果您仔细看一下芯片,您会发现这些参数对于HMOS I和HMOS III有何不同。板(取自HMOS III技术)总结了各种HMOS工艺的特点。对于每个版本,特征尺寸都会减小,而性能会提高。从HMOS-II升级到HMOS-III,英特尔的性能提高了40%。

| HMOS I | HMOS II | HMOS III | |

|---|---|---|---|

| 扩散步长(µ) | 8.0 | 6.4 | 5.0 |

| 多晶硅间距(µ) | 7.0 | 5.6 | 4.0 |

| 金属台阶(µ) | 11.0 | 8.0 | 6.4 |

| 气门氧化层厚度(Å) | 700 | 400 | 250 |

| 通道长度(µ) | 3.0 | 2.0 | 1.5 |

| Idsat(mA) | 8.0 | 14.0 | 27.0 |

| 最小阀延迟(ps) | 1000 | 400 | 200 |

| 散热阀延迟(pJ) | 1.0 | 0.5 | 0.25 |

| 线性降低率 | 1.0 | 0.8 | 0.64 |

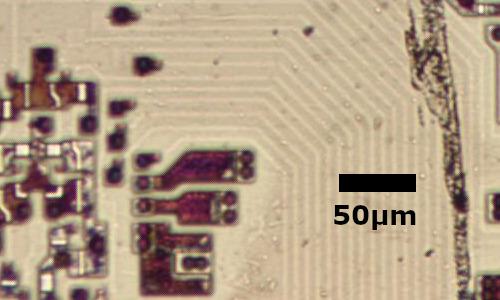

下图是通过显微镜拍摄的,显示了旧的8086芯片中晶体管的复杂排列。深色区域是带有杂质的硅,浅色矩形是晶体管的栅极。图为约21个晶体管。关键尺寸是通道长度,即阀从源极到漏极的长度(这是浅矩形的较小边)。对于这些,我测量了3 µm的长度,这与HMOS I公布的规格一致。为了进行比较,今天的处理器正在切换到5纳米,这是小600倍。

您可能已经注意到照片中的三个晶体管的栅极更大。这些晶体管用作上拉电阻,这是NMOS的典型特性。增大它们的尺寸会削弱晶体管的强度,因此上拉电流会很弱。

8086. . – , .

下图显示了相同尺寸的新型8086中的晶体管;您会看到晶体管的尺寸已经小得多。线性尺寸为原始尺寸的64%,因此与以前的晶体管相比,晶体管占据了40%的面积。我对该晶体进行了不同的处理,因此多晶硅保留在上面-这些是淡黄色的线。带有杂质的硅看起来是粉红色的,并且比上一张照片中的可见度更低。我确定阀门长度为1.9微米,是之前3微米的64%。注意,HMOS-III的沟道长度保持在1.5 µm的较短,但是,由于所有内容都减少了相同的次数,因此沟道长度比必要的更长。这表明均匀减少会导致新方法失去某些优势,但是这样做更容易。而不是从头开始设计新芯片。

新的8086芯片中的晶体管,在硅或多晶硅与金属层(此处已移去)之间有许多贯穿导体。

我还研究了金属层上轮胎之间的间距。下图显示了旧芯片的水平和垂直金属导体。我确定金属轮胎的间距为11微米,这与HMOS I的已发布特性相吻合。减小到64%可使新芯片上的间距达到7微米,尽管HMOS III工艺也支持6.4微米。与以前一样,相同的减少因子使您无法享受新流程的所有好处。

8086芯片的金属层,在金属下方可以看到带红色的多晶硅导体。

最后,我研究了多晶硅导体的间距。下图显示了旧的8086;多晶硅已被去除,只有淡淡的白线可见。这些平行的多晶硅线可能形成了一条总线,该总线将信号从芯片的一部分发送到另一部分。对于多晶硅,我测得的步长为7微米,与文档相符。有趣的是,由于HMOS的特性,多晶硅导体可以比金属导体更紧密地堆积在一起。新芯片的间距为4.5微米,尽管有可能使其尺寸为4微米。

多晶硅在旧的8086芯片上运行

结论

缩放晶体可以提高处理器的速度并降低其成本,而不会浪费从头设计的精力。但是,对这两个芯片的比较显示,缩放芯片比简单地缩小整个芯片要复杂得多。大多数电路只是收缩,但焊盘的收缩幅度不及其余电路,因此必须重新排列。功率分配也已更改,并且在芯片周围添加了更多的功率导体。

现代微处理器仍使用晶体缩放技术。在2007年,英特尔切换到了节拍模式,在该模式下,现有芯片(“ tick”)的缩放与新的微体系结构(“ tock”)的发布交替出现。

也可以看看: